# 要旨

近年 DRAM と NAND 型フラッシュメモリとのアクセス性能差を埋めるメモリとしてストレージクラスメモリ(storage class memory, SCM)が研究、開発されてきた.磁気抵抗型メモリ(magnetoresistive RAM, MRAM),抵抗変化型メモリ(resistive RAM, ReRAM),相変化メモリ(magnetoresistive RAM,MRAM)が SCM の主な候補である.SCM は DRAM と同じくバイトアクセス可能で,DRAM と同等の 0.1 µsec 未満のアクセス性能を持つ.一方で NAND 型フラッシュメモリと同じく不揮発であり,Single-level cell(SLC,1 bit/cell)NAND 型フラッシュメモリに近い 1-10 µsec 程度のアクセス性能を持つ SCM も存在する.本論文では,高速なアクセス性能を持つ SCM をメモリタイプ SCM(memory-type SCM,M-SCM)と呼び,NAND型フラッシュメモリに近い容量を達成するであろう SCM をストレージタイプ SCM(storage-type SCM,S-SCM)と呼ぶ.NAND型フラッシュメモリもまた多値化技術により大容量化が進んだが,その書き換え性能は低下する.本論文では不揮発性半導体メモリを複数種用いてデータを管理,保存するヘテロジニアスストレージシステムを提案する.データを保存する不揮発性の記憶媒体として,M-SCM,S-SCM および Multiple-level cell(MLC,2 bit/cell),Triple-level cell(TLC,3 bit/cell)NAND型フラッシュメモリを用いる.

本論文では三種以上の不揮発性半導体メモリを用い、二種類のヘテロジニアスストレージを提案する。また用いる不揮発性半導体メモリの特性に適したデータ管理アルゴリズムを提案する。SCM および MLC NAND 型フラッシュメモリを用いたハイブリッドストレージと比較して、第一の SCM、MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージは、SCM に頻繁にアクセスされるデータを保存し、MLC NAND 型フラッシュメモリに滞留するアクセス頻度の低いデータを TLC NAND 型フラッシュメモリに保存することで MLC および TLC NAND 型フラッシュメモリの寿命を延ばす。第二の M-SCM、S-SCMおよび NAND 型フラッシュメモリを用いたヘテロジニアスストレージは、SCM を二種類用いて極端にアクセス頻度の高いデータを M-SCMに、ややアクセス頻度の高いデータを S-SCMに保存することを特徴とする。これらの不揮発性半導体メモリの組み合わせを用いたストレージは性能が向上し、消費エネルギーが削減される。

一方でストレージアプリケーションは、読み出し・書き込み量の多寡、平均データアクセス頻度、平均データサイズなどの特性が異なる。したがってストレージアプリケーションの特性に対して、ヘテロジニアスストレージの適切な不揮発性半導体メモリの組み合わせが異

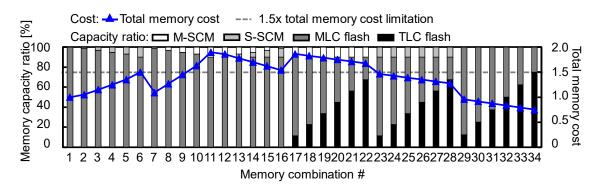

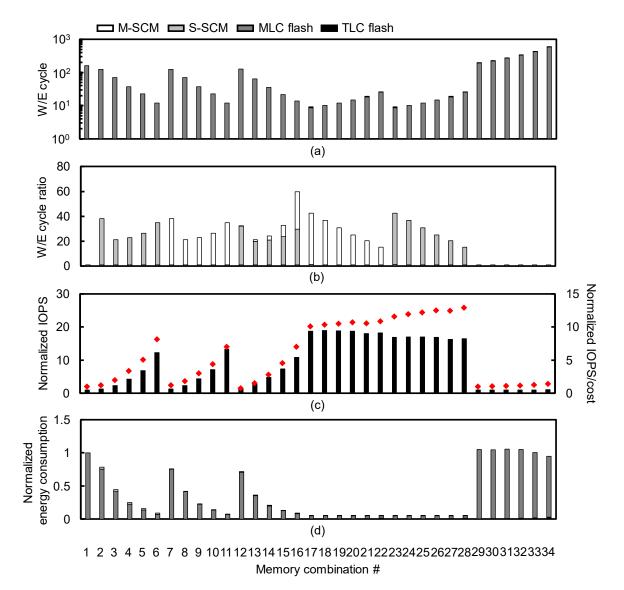

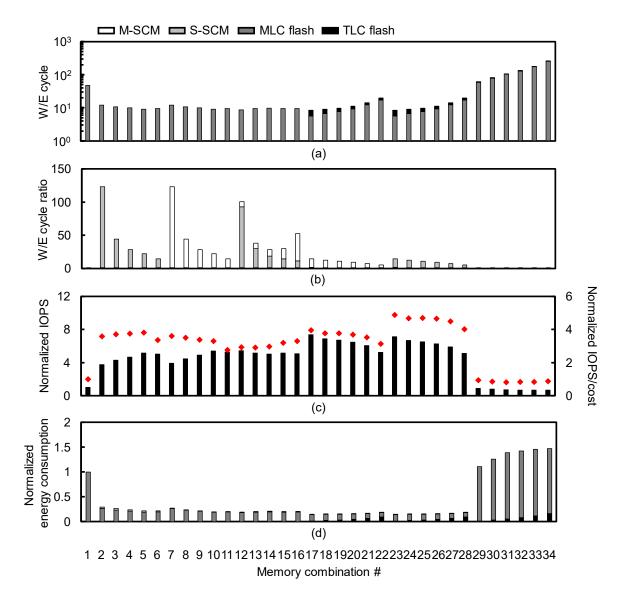

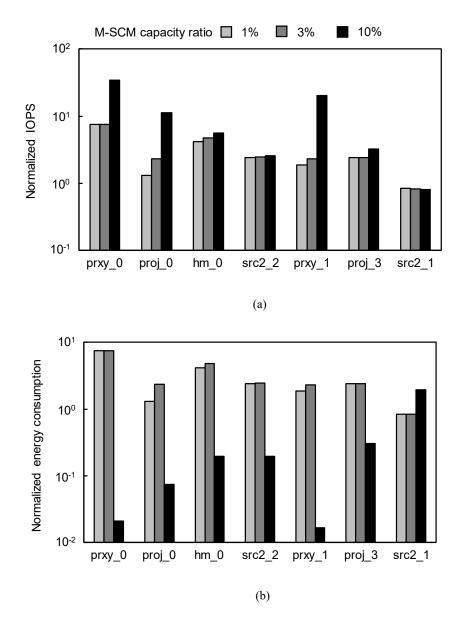

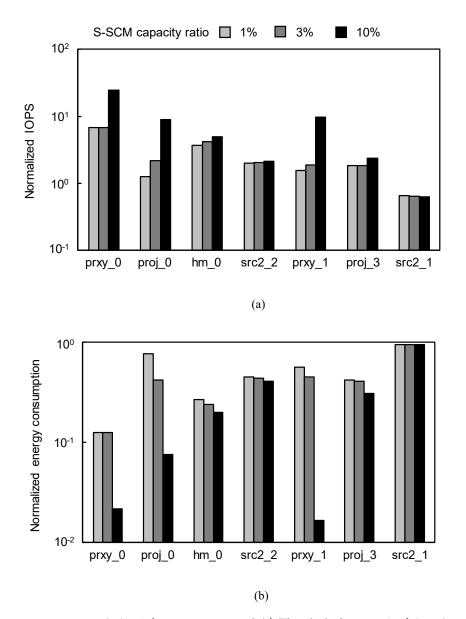

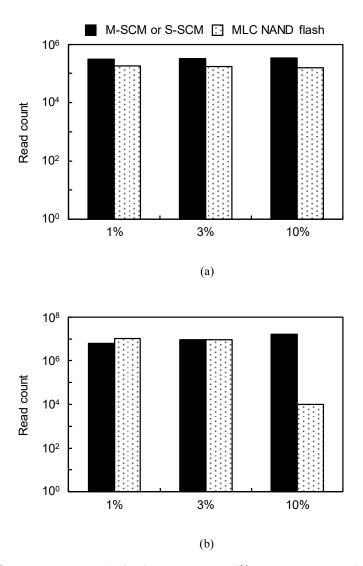

なる、不揮発性半導体メモリの特性および容量を変え、ベンチマークとするストレージアプ リケーションを用いた評価を行なった、その結果、高速な M-SCM を大容量用いるほどヘテ ロジニアスストレージの性能が向上することが明らかとなった. しかし単位容量当たりの M-SCM のコストは、NAND 型フラッシュメモリと比較して約10倍と予想される. そのため本 論文では、MLCNAND型フラッシュメモリのみを用いたストレージのコストと比較して、へ テロジニアスストレージは 1.5 倍のコスト増が許容できると仮定した. その結果, 読み出し・ 書き込み量の多寡および平均データサイズ(ランダム・シーケンシャル)と比較して、スト レージアプリケーションの平均データアクセス頻度(ホット・コールド)が、ヘテロジニア スストレージの最適な構成の決定に重要であることを明らかにした.一部のデータが頻繁に 書き換えられるストレージアプリケーションに対しては,S-SCM を大容量用いることで性能 を向上できることを明らかにした. あるいは M-SCM を極小容量用いて書き込み性能を向上 できることを明らかにした.また一部のデータが頻繁に読み出し・書き込みされるストレー ジアプリケーションに対しては、M-SCM を大容量用いることで性能を向上できることを明ら かにした. 一方で, 上書きおよび読み出しが頻繁に行われないアプリケーションに対しては, 小容量で高速な M-SCM を書き込みバッファとして機能させることが良いことを明らかにし た.

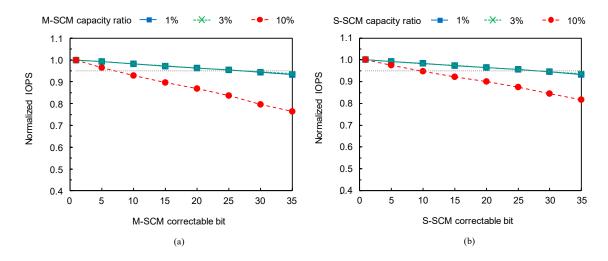

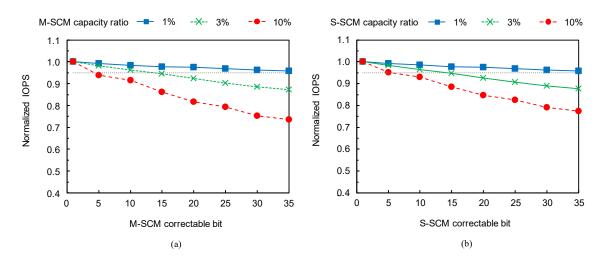

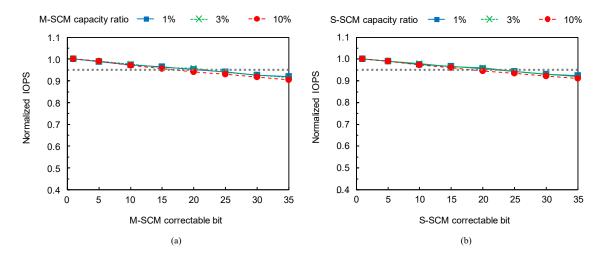

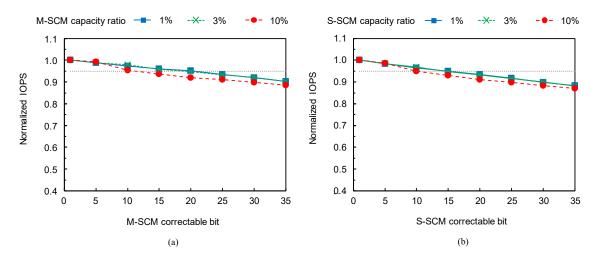

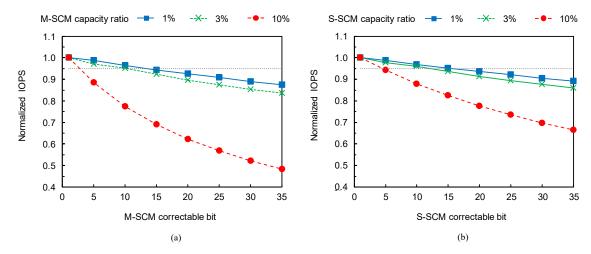

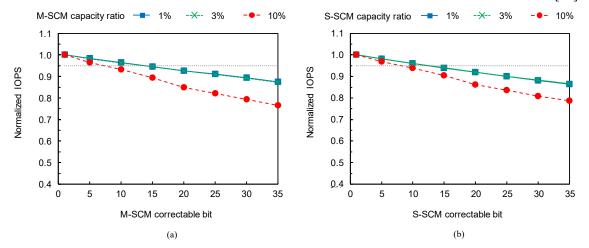

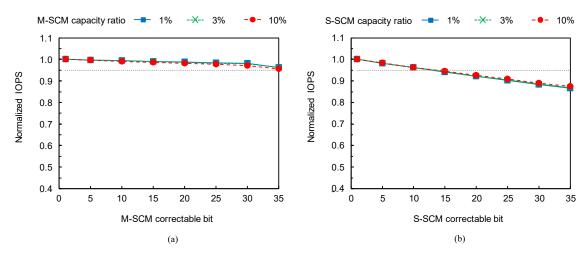

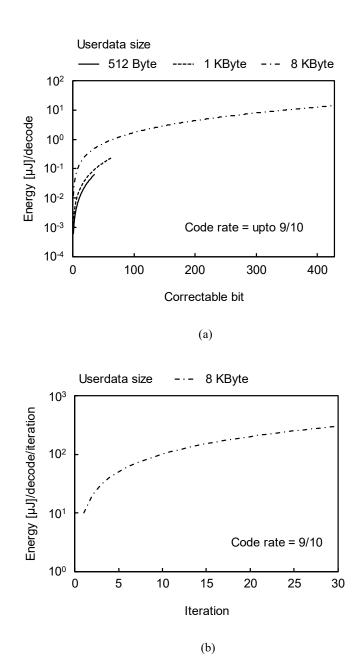

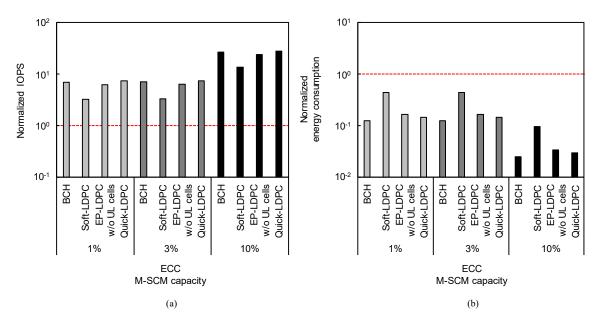

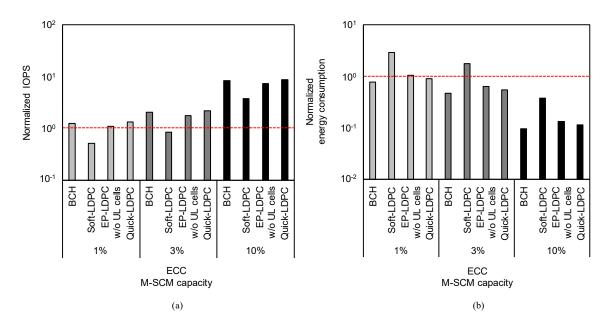

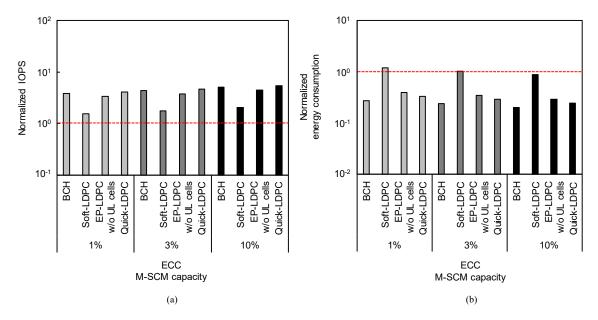

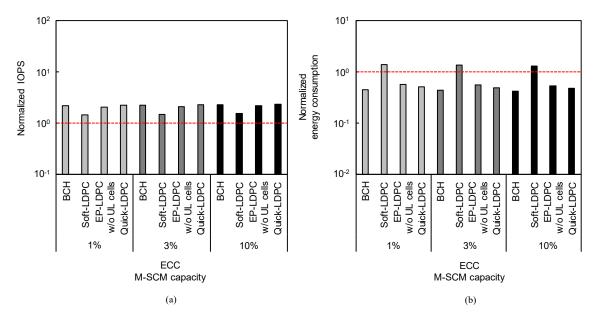

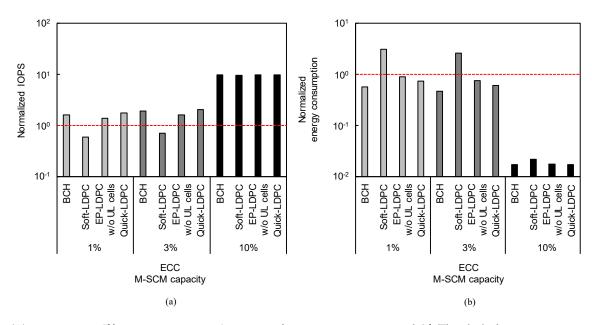

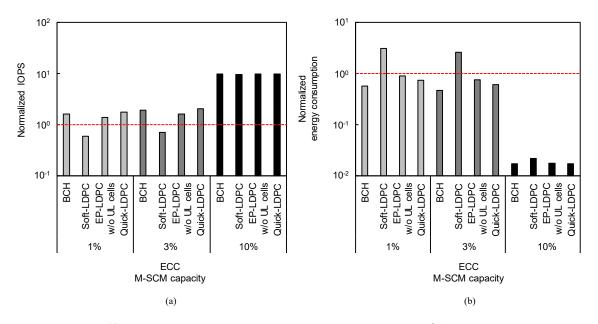

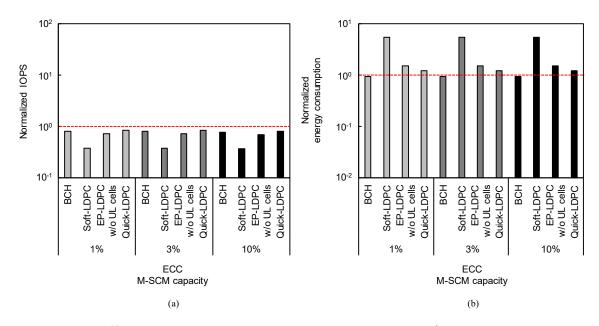

続いて、エラー訂正符号(error-correcting code、ECC)を用いて SCM および MLC NAND 型フラッシュメモリを用いたハイブリッドストレージの信頼性を向上させる。しかし ECC の復号によりストレージ性能は低下するトレードオフがある。不揮発性半導体メモリの種類によって信頼性は異なりまた許容書き換え回数も異なる。一部のデータが頻繁にアクセスされ、平均データサイズが小さいホット・ランダムアプリケーションに対して、大容量の SCM は性能を大きく向上させるが、SCM に適用する ECC 強度を弱くしなければ求められる性能を維持できない。これと比較して NAND 型フラッシュメモリは、大容量の SCM を用いるハイブリッドストレージでは多量のデータが SCM で処理されるため、復号時間の長い LDPC 符号を NAND 型フラッシュメモリに適用することを可能にすることを明らかにした。

最後にストレージアプリケーションに対して必要な SCM の容量を自律調整する手法を提案する. 頻繁にアクセスされるデータを SCM に保存することでストレージ性能は向上するが,適切な SCM 容量はストレージアプリケーションの特性によって異なる. また,複数のストレージアプリケーションが動作するデータセンターにおいて,それぞれのストレージアプリケーションに対して適切な SCM 容量を手動で決定することは実用的ではない. そこで M-SCM および MLC NAND 型フラッシュメモリを用いたハイブリッドストレージにおいて,

MLC NAND 型フラッシュメモリに保存されたデータのアクセス頻度を管理することで調整 すべき SCM の容量を判断することを提案する. その結果頻繁にアクセスされるデータが SCM に保存され、ストレージ性能を低下させることなく SCM の容量を調整できることを示した.

以上により、一部のデータが頻繁に書き込み、読み出されるストレージアプリケーションに対して高速な M-SCM が有効であることを明らかにした。また、やや頻繁に書き込み、読み出しが行われるアプリケーションに対しては、大容量で NAND 型フラッシュメモリより高速な S-SCM が必要であることを示した。一方で、上書きおよび読み出しが頻繁に行われないアプリケーションに対しては、小容量で高速な M-SCM を書き込みバッファとして機能させると良いことを明らかにした。

# 目次

| 要旨                                              | 1     |

|-------------------------------------------------|-------|

| 第1章 序論                                          | 6     |

| 1.1 研究の背景                                       | 6     |

| 1.2 本研究の目的                                      | 8     |

| 1.3 本論文の構成                                      | 9     |

| 参考文献                                            |       |

| 第2章 次世代コンピュータアーキテクチャにおけるストレージの研究課題              | 16    |

| 2.1 はじめに                                        | 16    |

| 2.2 次世代コンピュータアーキテクチャ                            | 16    |

| 2.3 不揮発性半導体メモリ                                  | 18    |

| 2.3.1 NAND 型フラッシュメモリ                            | 19    |

| 2.3.2 ストレージクラスメモリ (SCM)                         | 25    |

| 2.4 SCM および NAND 型フラッシュメモリを用いたストレージ             | 28    |

| 2.4.1 SCM および NAND 型フラッシュメモリを用いたハイブリッドストレージ     | 29    |

| 2.4.2 MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレージ |       |

| 2.5 次世代コンピュータアーキテクチャにおけるストレージの課題                | 35    |

| 2.6 まとめ                                         | 39    |

| 参考文献                                            | 40    |

| 第3章 異種の不揮発性メモリを用いたストレージ構成およびデータ管理アルゴリズム         | 46    |

| 3.1 はじめに                                        | 46    |

| 3.2 不揮発性メモリの読み出し、書き込み時間                         | ·· 46 |

| 3.3 SCM, MLC および TLC NAND 型フラッシュメモリを用いたストレージ    | 49    |

| 3.4 M-SCM, S-SCM および NAND 型フラッシュメモリを用いたストレージ    | 53    |

| 3.5 まとめ                                         | 57    |

| 参考文献                                            | 58    |

| 第4章 アプリケーションに応じた不揮発性メモリの選択                      | 59    |

# 第1章 序論

#### 1.1 研究の背景

近年 Internet of Things(IoT)や機械学習技術の興隆によりデータセンターでは、種類、速度、量など特徴の異なる多種多様なデータが実行される[1][2]. 自動運転車、インダストリ 4.0、セキュリティシステムのような IoT アプリケーションではネットワークのエッジで収集した温度や画像などのデータをデータセンターで処理する。データセンターに集められたデータはたとえば機械学習技術を用いて多量のデータから類似するパターンを発見、モデル化し、将来の予測を行う。これらのデータは大きさやアクセスパターンなどの特徴がそれぞれ異なるため、ストレージに必要な特性も異なる。データセンターでは現在、高速な NAND 型フラッシュメモリを用いたソリッドステートドライブ(solid-state drive、SSD)などのストレージがハードディスクドライブ(hard-disk drive、HDD)を置き換えつつある。さらに HDD は書き込み・読み取り部に機械部品を用いるため衝撃に弱く故障が予測できない。一方で NAND型フラッシュメモリは不揮発性半導体メモリであるため機械部品は使われず、データ書き換えやデータ保持によりビット反転が発生し、データの書き込み・読み出しエラーの原因となる。

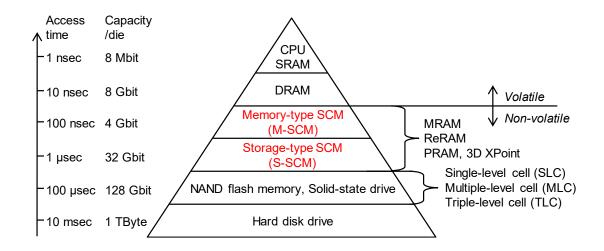

図 1.1 にメモリおよびストレージ階層を示す[3][4][5][6][7][8][9]. 階層の上から下へメモリのアクセス性能は低下する. その一方でメモリダイ(メモリチップ)当たりの容量は増加するため、ビットコストは低減する. 上層の static random access memory(static RAM, SRAM)および dynamic RAM(DRAM)は揮発メモリであり電源消失によりデータが失われるが、高速に書き換え可能である. SRAM はデータ記憶にフリップフロップ回路を用い、6 トランジスタで構成されるため回路面積が必要でビットコストが高い. そのため小容量で十分なプロセッサのキャッシュメモリなどで用いられる. DRAMのメモリセルはトランジスタとキャパシタによって構成され、キャパシタの電荷を保存することでデータ保持を行う. リーク電流によりキャパシタ内の電荷が失われるとデータが失われるため、常に電源供給が必要で、さらにデータ消失を防ぐために定期的なデータリフレッシュを行う. 常に電源供給が必要なことおよび定期的なデータリフレッシュを行うことから、DRAM は SRAM と比較して消費電力

図 1.1 メモリおよびストレージ階層 [3][4][5][6][7][8][9]

が高い. しかしながら微細化によってビットコストが低減し続けたため, DRAM はキャッシュよりも大容量が必要な主記憶(メインメモリ)として用いられる. さらにまた DRAM を不揮発化するために電池を用い, 瞬断に対応した battery back-uped (BBU) DRAM がある.

メモリおよびストレージ階層の下層に位置するストレージクラスメモリ(storage class memory, SCM)および NAND 型フラッシュメモリは不揮発であり,電源を消失してもデータは失われないため恒常的な電源供給は不要である.代表的な不揮発性半導体メモリであるNAND 型フラッシュメモリは,メモリおよびストレージ階層(図 1.1)の最下層に位置する.NAND 型フラッシュメモリのセルは P 型半導体の上に構成された MOSFET であり,浮遊ゲートに電子を注入することでデータを保存する.浮遊ゲートは電気的に浮遊しているため電源を失ってもデータを保存できる.NAND 型フラッシュメモリは微細化および多値化技術により大容量化・ビットコスト低減が進められてきた.一方で多値化技術により Multiple-level cell(MLC)NAND 型フラッシュメモリ,Triple-level cell(TLC)NAND 型フラッシュメモリが実現した[10][11].多値化技術は NAND 型フラッシュメモリを大容量化した一方で,そのアクセス性能および信頼性は低下する[12].NAND 型フラッシュメモリはその大容量・低ビットコストによって携帯可能な USB メモリおよびメモリカード,個人向けコンピュータの二次記憶としての SSD や,さらにアクセス性能および大容量が求められるデータセンターのストレージとして用いられる.しかし DRAM と NAND 型フラッシュメモリとの間には約 10<sup>4</sup>倍のアクセス性能差がある.

このため DRAM と NAND 型フラッシュメモリとのアクセス性能差を埋めるメモリとして

SCM が研究, 開発されてきた[13][14]. 磁気抵抗メモリ (magnetoresistive RAM, MRAM) [15][16], 抵抗変化型メモリ (resistive RAM, ReRAM) [6][17][18], 相変化メモリ (phase change RAM, PRAM) [7][19][20]が SCM の主な候補である. SCM は DRAM と同じくバイトアクセス可能で, DRAM と同等のアクセス性能を持つ. 一方で NAND 型フラッシュメモリと同じく不揮発であり, SLC NAND 型フラッシュメモリに近いアクセス性能を持つ. 近年ではさらに SCM はその特性によりメモリタイプ SCM (memory-type SCM, M-SCM) およびストレージタイプ SCM (storage-type SCM, S-SCM) に細分化されている[21]. 本論文では MRAM は高速なアクセス性能を持つため M-SCM と呼び, ReRAM および PRAM は大容量であるため S-SCM と呼ぶ. しかし SCM は開発途上であり、そのデータ保持方式などから NAND 型フラッシュメモリと同等に大容量化することは難しく SCM 単体でストレージとして使うにはコストが高い. さらにここに述べたように性能、信頼性、コストすべての面で優れたユニバーサルメモリは現在存在しない.

# 1.2 本研究の目的

本研究では第 1.1 節で述べたさまざまな不揮発性半導体メモリを組み合わせ、異種の不揮発性半導体メモリで構成されるヘテロジニアスストレージを提案する。ストレージアプリケーションは書き込み・読み出しの多寡、データアクセス頻度、データアクセスサイズなどの点でそれぞれ特性が異なる。また不揮発性半導体メモリはアクセス速度、信頼性、書き換え耐久性(許容書き換え回数)、コストなどの点でそれぞれ異なる特性を持つ。そのため特性の異なるストレージアプリケーションに最適な不揮発性半導体メモリの構成および要件を提示する。従来研究として SCM および NAND 型フラッシュメモリを用いたハイブリッドストレージが提案されている[22][23][24]。 NAND 型フラッシュメモリの低速な書き込み速度を隠ぺいするため、SCM は不揮発性キャッシュメモリあるいは小容量ストレージとして用いる。また SCM を用いた SSD [25]は NAND 型フラッシュメモリを用いた SSD の不揮発性キャッシュとして期待されている。これらの従来技術では二種類の不揮発性半導体メモリを用いてストレージを構成する。

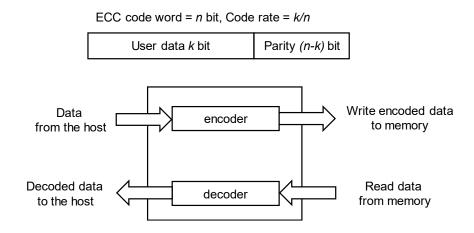

不揮発性半導体メモリは HDD と異なり突然の機械部品の故障は起きないが、データの書き換えやデータ保持などにより徐々にエラーが発生する. 不揮発性半導体メモリの種類によって信頼性は異なりまた書き換え耐久性(許容書き換え回数)も異なる. ストレージコントローラ内のエラー訂正回路が不揮発性半導体メモリに生じたエラーを訂正する. エラー訂正

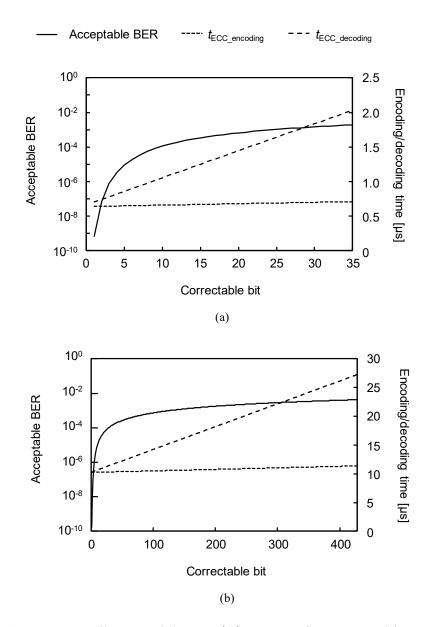

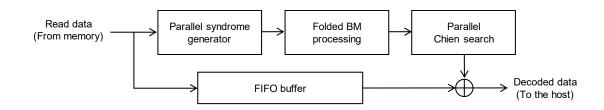

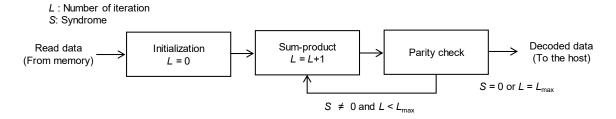

回路はエラー訂正符号(error-correcting code, ECC)の種類によって異なる。ECC は書き込みたいデータにパリティを付加してデータを符号化してメモリに書き込む。またメモリからの読み出し時にデータ復号しエラー訂正を行う。一般に書き込み時の符号化と比較して読み出し時の復号に時間がかかる。さらに、エラー訂正能力の高い ECC はエラー訂正能力の低いECC と比較して、ECC の動作に長い時間を要する。本論文では、SCM および NAND 型フラッシュメモリを用いたストレージについて、エラー訂正能力の異なる ECC を適用し高信頼化を図る。一方で ECC によるストレージ性能の低下を評価し、SCM および NAND 型フラッシュメモリに適用可能な ECC の強度を見積もる。

さらに異種の不揮発性半導体メモリを用いたストレージの不揮発性半導体メモリ構成の自動最適化を行う. 頻繁にアクセスされるデータを含むアプリケーションほど多量の SCM を必要とする一方で, 頻繁にアクセスされるデータが少ないアプリケーションは多量の SCM を用いてもストレージ性能に寄与しない. データセンターではさまざまなストレージアプリケーションが動作するため, それぞれのアプリケーションに対し適切な不揮発性半導体メモリの容量を手動で決定することは不可能である. また SCM のビットコストは NAND 型フラッシュメモリのそれと比較して高価であるため, アプリケーションが必要な場合にのみ SCM を用いたい. そのためストレージコントローラがストレージアプリケーションの特性を把握し,随時必要な SCM 容量を調整することが必要である.

以上により、不揮発性半導体メモリの特性およびストレージアプリケーションの特性を考慮し、高速、高信頼、低コストなヘテロジニアスストレージを構築することを目的とする.

#### 1.3 本論文の構成

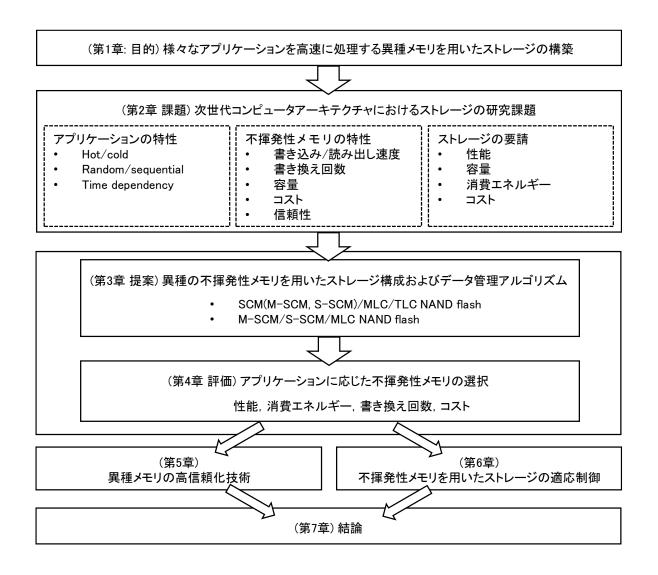

本論文は全7章から成る.図1.2に本論文の構成を示す.第1章では研究の背景と目的について述べた.ストレージクラスメモリ(storage class memory、SCM)と呼ばれる新規の不揮発性半導体メモリの登場によってメモリおよびストレージ階層が多層化しつつある.またストレージアプリケーションの特性はさまざまに異なるため、アプリケーションの特性に応じたストレージ構成が必要であることを述べた.さらに不揮発性半導体メモリに発生するエラーを訂正するためにエラー訂正符号(error-correcting code、ECC)が不可欠であるが、ECCによりストレージ性能が低下するため不揮発性半導体メモリに適用可能な ECC 強度を見積もることを述べた.またストレージアプリケーションの特性によって必要な SCM 容量は異なり、SCM のビットコストは NAND 型フラッシュメモリと比較して高価であるため、SCM 容量の自動最適化が必要であることを述べた.

図 1.2 本論文の構成

第2章では不揮発性半導体メモリを用いたストレージの従来研究および問題点について述べる。まず初めに不揮発性半導体メモリである SCM と NAND 型フラッシュメモリの動作について述べる。SCM はその特性によってメモリタイプおよびストレージタイプに分類でき、一方で NAND 型フラッシュメモリはセル当たりに保存するビット数によって SLC、MLC、TLC に分類できることを示す。従来研究として SCM 一種および NAND 型フラッシュメモリー種を用いたハイブリッドストレージストレージの構成、および SCM を NAND 型フラッシュメモリーを用いたハイブリッドストレージストレージの構成、および SCM を NAND 型フラッシュメモリの不揮発性キャッシュあるいは小容量ストレージとして用いるデータマネジメント手法について説明する。さらに不揮発性半導体メモリを用いた次世代のコンピュータアーキテクチャにおけるストレージの課題を論じる。第1章で述べたようにストレージアプリケーションの特性がさまざまに異なるためストレージアプリケーション内のデータの特徴によって、異種の不揮発性半導体メモリを用いたヘテロジニアスストレージの不揮発性半導体メモ

リの構成の最適化が必要となる。またヘテロジニアスストレージの SCM と NAND 型フラッシュメモリとではアクセス頻度が異なり、不揮発性半導体メモリの種類によってエラー発生頻度や許容書き換え回数が異なるため、それぞれに異なる強度の ECC を適用することが必要となる。さらにストレージアプリケーションの特性によって最適な SCM 容量は異るが、データセンター事業者やユーザが手動でさまざまな種類のストレージアプリケーションに必要なSCM 容量を設定することは困難であるため、自動で SCM 容量を最適化する手法が必要であることを述べる。

第3章では異種の不揮発性半導体メモリを用いたヘテロジニアスストレージ構成を提案す る. 従来研究と異なり、三種以上の不揮発性半導体メモリを用いて構成したストレージをへ テロジニアスストレージと呼び本論文で扱う. ヘテロジニアスストレージとして, 1) SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージおよび 2) M-SCM, S-SCM および NAND 型フラッシュメモリを用いたヘテロジニアスストレージを提 案する.第一の SCM,MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアス ストレージは、SCM および MLC NAND 型フラッシュメモリを用いたハイブリッドストレー ジと比較して, MLC NAND 型フラッシュメモリに滞留するアクセス頻度の低いデータを TLC NAND 型フラッシュメモリに保存することで MLC NAND 型フラッシュメモリの書き換え回 数を削減することを目的とする. さらに SCM の導入で上昇する総ストレージコストをビット コストの低い TLC NAND 型フラッシュメモリでバランスできる. 第二の M-SCM, S-SCM お よび NAND 型フラッシュメモリを用いたヘテロジニアスストレージは、SCM を二種類用い て極端にアクセス頻度の高いデータを M-SCM に,ややアクセス頻度の高いデータを S-SCM に保存することを特徴とする. M-SCM は S-SCM と比較して高速だがビットコストが高いた め、ごく少量のデータが頻繁にアクセスされるストレージアプリケーションに適していると 考える.

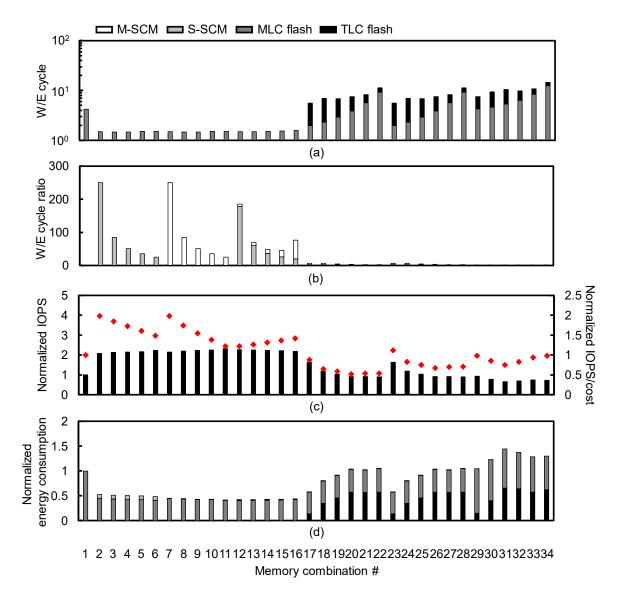

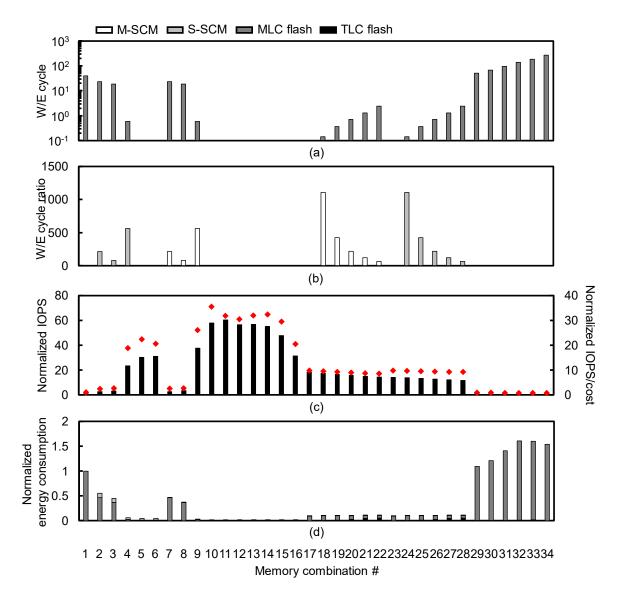

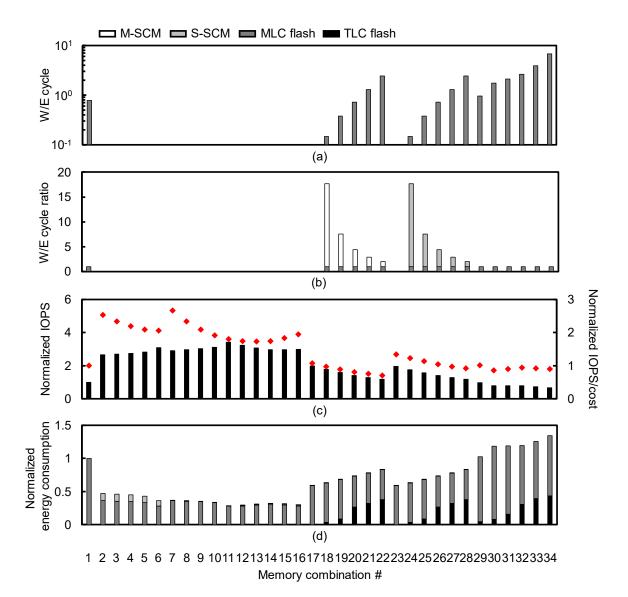

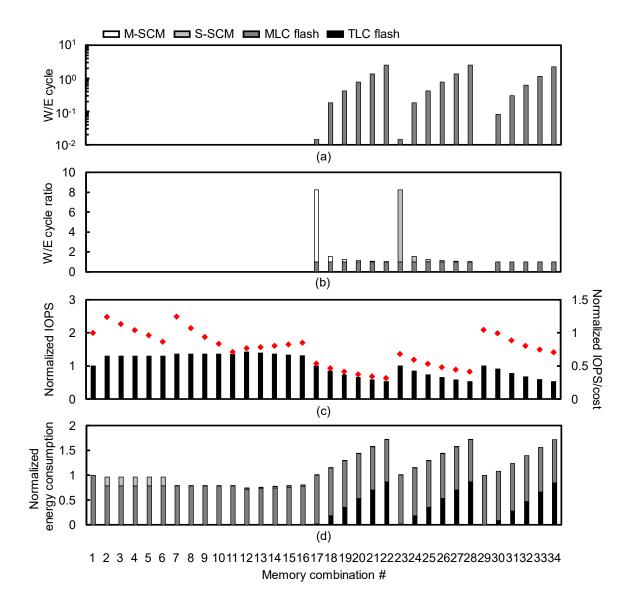

第4章では、第3章で提案した二種類のヘテロジニアスストレージの評価を行なう. SystemC ベースのストレージエミュレータに、不揮発性半導体メモリの動作およびデータマネジメントアルゴリズムを実装した. 不揮発性半導体メモリの容量比や書き込み・読み出し時間などのアクセス性能を変化させ、ヘテロジニアスストレージのアクセス性能、消費エネルギー、不揮発性半導体メモリの書き換え回数の点から評価し比較する. 代表的なストレージアプリケーション毎にヘテロジニアスストレージの最適な不揮発性半導体メモリ構成を示す.

第5章では異種メモリの高信頼化技術について述べる. ここでは SCM および NAND 型フ

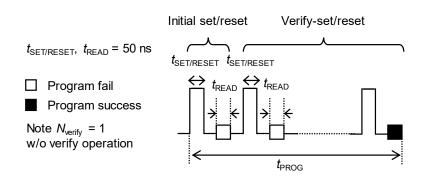

ラッシュメモリを用いたハイブリッドストレージに強度の異なる ECC を適用する. NAND 型フラッシュメモリには従来から Bose-Chaudhuri-Hocquenghem (BCH) 符号が用いられている. BCH 符号は高速でランダムエラーを訂正できる ECC であるため,ストレージとして用いる SCM にも適用する.また NAND 型フラッシュメモリの微細化および多値化が進むにつれ,BCH 符号より訂正能力の高い low-density parity-check (LDPC) 符号も適用されつつある.これらの ECC を不揮発性半導体メモリに用いるとストレージ性能が低下するため,ハイブリッドストレージで用いる SCM および NAND 型フラッシュメモリに適用できる ECC の強度を示す.

第6章ではストレージアプリケーションの特性に応じた SCM 容量の自律調整手法を述べる. SCM と NAND 型フラッシュメモリを用いたハイブリッドストレージは、ストレージアプリケーションの性質によって必要となる SCM 容量は異なる. さまざまな特性を持つストレージアプリケーションに最適な SCM 容量をそれぞれ手動で決定することは難しい. SCM から NAND型フラッシュメモリへ移されたデータの中で頻繁にアクセスされるデータをゴースト least recently used (ghost LRU) リストを用いて検出し拡大すべき SCM 容量を計算する手法について述べる. また SCM 内で頻繁にアクセスされるデータを NAND 型フラッシュメモリへ移動することを防ぐアルゴリズムについても述べ、ハイブリッドストレージ性能を評価する.

第7章に本論文の結論と今後の研究について展望を述べる。本論文ではストレージアプリケーションの特性に応じた異種の不揮発性半導体メモリを用いたヘテロジニアスストレージの最適な構成を論じた。極頻繁にアクセスされるデータを含むストレージアプリケーションには高速な M-SCM が必要である。一方で頻繁にアクセスされないデータを含むストレージアプリケーションは TLC NAND 型フラッシュメモリが必要であることがわかる。また SCM および NAND 型フラッシュメモリを用いたストレージにおいて、SCM 容量が多いと SCM へのアクセス頻度が増すために SCM に適用する ECC の強度は一定以下に抑えねばならず、しかし NAND 型フラッシュメモリへのアクセス頻度は減少するために NAND 型フラッシュメモリに適用する ECC の強度を強めることができる。さらに SCM 容量の自律調整手法を用いることで、ストレージ動作期間中のストレージコストを抑えることができることを示す。最後に3次元積層された NAND 型フラッシュメモリを用いた場合のヘテロジニアスストレージのデータマネジメントアルゴリズム最適化や、SCM 容量調整手法に機械学習を用いることが今後の研究課題であることを述べる。

# 参考文献

- [1] M. Fink, "Toward a memory-centric architecture," in Flash Memory Summit, 2017.

- [2] EMC Digital Universe with Research & Analysis by IDC, "The Digital Universe of Opportunities: Rich Data and the Increasing Value of the Internet of Things," Apr. 2014, http://www.emc.com/leadership/digital-universe/2014iview/business-imperatives.htm.

- [3] M. Yabuuchi, K. Nii, S. Tanaka, Y. Shinozaki, Y. Yamamoto, T. Hasegawa, H. Shinkawata, and S. Kamohara, "A 65 nm 1.0 V 1.84 ns Silicon-on-Thin-Box (SOTB) embedded SRAM with 13.72 nW/Mbit standby power for smart IoT," in *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, Jun. 2017, pp. 220-221.

- [4] K. Song, S. Lee, D. Kim, Y. Shim, S. Park, B. Ko, D. Hong, Y. Joo, W. Lee, Y. Cho, W. Shin, J. Yun, H. Lee, J. Lee, E. Lee, N. Jang. J. Yang, H.-K. Jung, J. Cho, H. Kim, and J. Kim, "A 1.1 V 2y-nm 4.35 Gb/s/pin 8 Gb LPDDR4 mobile device with bandwidth improvement techniques," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 50, no. 8, pp. 1945-1959, Aug. 2015.

- [5] S.-W. Chung, T. Kishi, J. W. Park, M. Yoshikawa, K. S. Park, T. Nagase, K. Sunouchi, H. Kanaya, G. C. Kim, K. Noma, M. S. Lee, A. Yamamoto, K. M. Rho, K. Tsuchida, S. J. Chung, J. Y. Li, H. S. Chun, H. Oyamatsu, and S. J. Hong, "4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure," in *IEEE International Electron Devices Meeting (IEDM) Technical Digest*, Dec. 2016, pp. 27.1.1-27.1.4.

- [6] T.-Y. Liu, T. H. Yan, R. Scheuerlein, Y. Chen, J. K. Lee, G. Balakrishnan, G. Yee, H. Zhang, A. Yap, J. Ouyang, T. Sasaki, A. Al-Shamma, C. Chen, M. Gupta, G. Hilton, A. Kathuria, V. Lai, M. Matsumoto, A. Nigam, A. Pai, J. Pakhale, C. H. Siau, X. Wu, Y. Yin, N. Nagel, Y. Tanaka, M. Higashitani, T. Minvielle, C. Gorla, T. Tsukamoto, T. Yamaguchi, M. Okajima, T. Okamura, S. Takase, H. Inoue, and L. Fasoli, "A 130.7-mm2, 2-layer 32Gb ReRAM memory device in 24-nm technology," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 49, no. 1, pp. 140-153, Jan. 2014.

- [7] Micron 3D XPoint Technology, https://www.micron.com/about/emerging-technologies/3d-xpoint-technology.

- [8] M. Helm, J.-K. Park, A. Ghalam, J. Guo, C. W. Ha, C. Hu, H. Kim, K. Kavalipurapu, E. Lee, A. Mohammadzadeh, D. Nguyen, V. Patel, T. Pekny, B. Saiki, D. Song, J. Tsai, V. Viajedor, L. Vu, T. Wong, J. H. Yun, R. Ghodsi, A. D'Alessandro, D. Di Cicco, V. Moschiano, "A 128Gb MLC NAND-flash device using 16nm planer cell," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 2014, pp. 326-327.

- [9] G. Naso, L. Botticchio, M. Castelli, C. Cerafogli, M. Cichocki, P. Conenna, A. D'Alessandro, L.

- De Santis, D. Di Cicco, W. Di Francesco, M. L. Gallese, G. Gallo, M. Incarnati, C. Lattaro, A, Macerola, G. Marotta, V. Moschiano, D. Orlandi, F. Paolini, S. Perugini, L. Pilolli, P. Pistilli. G. Rizzo, F. Rori, M. Rossini, G. Santin, E. Sirizotti, A. Smaniotto, U. Siciliani, M. Tiburzi, R. Meyer, A. Goda, B. Filipiak, T. Vali, M. Helm, and R. Ghodsi, "A 128Gb 3b/cell NAND flash design using 20nm planer-cell technology," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 2013, pp. 218-219.

- [10] M. Bauer, R. Alexis, G. Atwood, B. Baltar, A. Fazio, K. Frary, M. Hensel, M. Ishac, J. Javanifard, M. Landgraf, D. Leak, K. Loe, D. Mills, P. Ruby, R. Rozman, S. Sweha, S. Talreja, and K. Wojciechowski, "A multilevel-cell 32Mb flash memory," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 1995, pp. 132-133.

- [11] K. Takeuchi, T. Tanaka, and T. Tanzawa, "A multi-page cell architecture for high-speed programming multi-level NAND flash memories," in *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, Jun. 1997, pp. 67-68.

- [12] HP, "Solid state drive technology: Differences between SLC, MLC and TLC NAND," http://h10032.www1.hp.com/ctg/Manual/c03757461.pdf, May 2013, Rev. 1.

- [13] R. F. Freitas and W. W. Wilcke, "Storage-class memory: The next storage system technology," *IBM Journal of Research and Development*, vol. 52, no. 4/5, pp. 439-447, Jul. 2008.

- [14] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "Overview of candidate device technologies for storage-class memory," *IBM Journal of Research and Development*, vol. 52, no. 4/5, pp. 449-464, Jul. 2008.

- [15] K. Tsuchida, T. Inaba, K. Fujita, Y. Ueda, T. Shimizu, Y. Asao, T. Kajiyama, M. Iwayama, K. Sugiura, S. Ikegawa, T. Kishi, T. Kai, M. Amano, N. Shimomura, H. Yoda, and Y. Watanabe, "A 64Mb MRAM with clamped reference and adequate-reference schemes," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 2010, pp. 258-259.

- [16] S.-W. Chung, T. Kishi, J. W. Park, M. Yoshikawa, K. S. Park, T. Nagase, K. Sunouchi, H. Kanaya, G. C. Kim, K. Noma, M. S. Lee, A. Yamamoto, K. M. Rho, K. Tsuchida, S. J. Chung, J. Y. Li, H. S. Chun, H. Oyamatsu, and S. J. Hong, "4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure," in *IEEE International Electron Devices Meeting (IEDM) Technical Digest*, Dec. 2016, pp. 27.1.1-27.1.4.

- [17] A. Kawahara, R. Azuma, Y. Ikeda, K. Kawai, Y. Katoh, K. Tanabe, T. Nakamura, Y. Sumimoto, N. Yamada, N. Nakai, S. Sakamoto, Y. Hayakawa, K. Tsuji, S. Yoneda, A. Himeno, K. Origasa, K. Shimakawa, T. Takagi, T. Mikawa, and K. Aono, "An 8Mb multi-layered cross-point ReRAM

- macro with 43 MB/s write throughput," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 48, no. 1, pp. 178-185, Oct. 2013.

- [18] K. Kawai, A. Kawahara, R. Yasuhara, S. Muraoka, Z. Wei, R. Azuma, K. Tanabe, and K. Shimakawa, "Highly-reliable TaOx ReRAM technology using automatic forming circuit," in Proceedings of IEEE International Conference on IC Design and Technology (ICICDT), May 2014, pp. 100-103.

- [19] K.-J. Lee, B.-H. Cho, W.-Y. Cho, S. Kang, B.-G. Choi, H.-R. Oh, C.-S. Lee, H.-J. Kim, J.-M. Park, Q. Wang, M.-H. Park, Y.-H. Ro, J.-Y. Choi, K.-S. Kim, Y.-R. Kim, I.-C. Shin, K.-W. Lim, H.-K. Cho, C.-H. Choi, W.-R. Chung, D.-E. Kim, Y.-J. Yoon, K.-S. Yu, G.-T. Jeong, H.-S. Jeong, C.-K. Kwak, C.-H. Kim, K. Kim, "A 90nm 1.8 V 512 Mb diode-switch PRAM with 266 MB/s read throughput," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 43, no. 1, pp. 150-162, Jan. 2008.

- [20] Y. Choi, I. Song, M. Park, H. Chung, S. Chang, B. Cho, J. Kim, Y. Oh, D. Kwon, J. Sunwoo, J. Shin, Y. Rho, C. Lee, M. G. Kang, J. Lee, Y. Kwon, S. Kim, J. Kim, Y. Lee, Q. Wang, S. Cha, S. Ahn, H. Horii, J. Lee, K. Kim, H. Joo, K. Lee, Y. Lee, J. Yoo, and G. Jeong, "A 20nm 1.8V 8Gb PRAM with 40MB/s program bandwidth," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 2012, pp. 46-47.

- [21] IBM Almaden Research Center, "Storage class memory: Towards a disruptively low-cost solid-state non-volatile memory," http://researcher.watson.ibm.com/researcher/files/us-gwburr/Almaden SCM overview Jan2013.pdf, Jan. 2013.

- [22] H. Fujii, K. Miyaji, K. Johguchi, K. Higuchi, C. Sun, and K. Takeuchi, "x11 performance increase, x6.9 endurance enhancement, 93% energy reduction of 3D TSV-integrated hybrid ReRAM/MLC NAND SSDs by data fragmentation suppression,"in *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, Jun. 2012, pp. 134-135.

- [23] C. Sun, K. Miyaji, K. Johguchi, and K. Takeuchi, "A high performance and energy-efficient cold data eviction algorithm for 3D-TSV hybrid ReRAM/MLC NAND SSD," *IEEE Transactions on Circuits and Systems-I (TCAS-I)*, vol. 61, no. 2, pp. 382-392, Feb. 2014.

- [24] S. Okamoto, C. Sun, S. Hachiya, T. Yamada, Y. Saito, T. O. Iwasaki, and K. Takeuchi, "Application driven SCM and NAND flash hybrid SSD design for data-centric computing system," in *Proceedings of IEEE International Memory Workshop (IMW)*, May 2015, pp. 157-160.

- [25] Intel Optane Technology, http://www.intel.com/content/www/us/en/architecture-and-technology/intel-optane-technology.html.

# 第2章 次世代コンピュータアーキテクチャに おけるストレージの研究課題

#### 2.1 はじめに

本章では不揮発性半導体メモリを用いたストレージの従来研究および次世代のコンピュータアーキテクチャにおけるストレージの研究課題について述べる。まず不揮発性半導体メモリであるストレージクラスメモリ(storage class memory, SCM)と NAND 型フラッシュメモリの動作および特性について述べる。SCM はその特性によってメモリタイプおよびストレージタイプに分類でき、一方で NAND 型フラッシュメモリはセル当たりに保存するビット数によって異なる特性を持つことを示す。続いて、新しい不揮発性半導体メモリである SCM を用いた次世代のコンピュータアーキテクチャについて述べる。SCM を用いたストレージに関するこれまでの研究状況について述べ、次世代のコンピュータアーキテクチャにおけるストレージの研究課題を論じる。

#### 2.2 次世代コンピュータアーキテクチャ

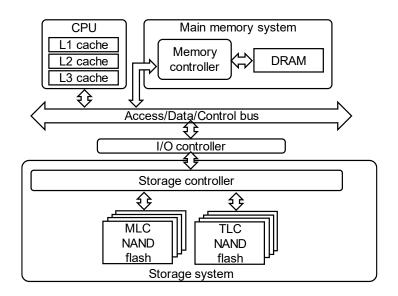

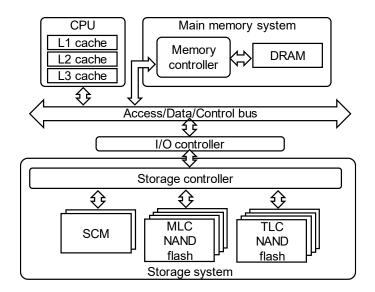

図 2.1 現在のノイマン型コンピュータアーキテクチャ

ャッシュに保存する.メインメモリとして高速で比較的大容量な dynamic RAM(DRAM)が用いられる. DRAM はキャパシタに電荷を保存することでデータを保持するため、電源を消失するとデータを失う。またリーク電流により電荷が失われるとデータのエラーが発生するため、定期的なデータリフレッシュを行う必要がある. DRAM は SRAM キャッシュと比較して十分大容量であるが、DRAM 内の頻繁にアクセスされないデータは二次記憶に移動し保存する. 二次記憶として従来ハードディスクドライブ(hard-disk drive、HDD)が用いられてきたが機械部品による突然の故障が発生する. そのため HDD は不揮発性半導体メモリであるNAND型フラッシュメモリを用いたソリッドステートドライブ(solid-state drive、SSD)に置き換わりつつある. このようにノイマン型コンピュータでは、CPU とメモリ間のデータ転送時の衝突やアクセス性能差がコンピュータアーキテクチャ全体の性能のボトルネックとなる. これをフォンノイマン・ボトルネック(von Neumann bottleneck)と呼ぶ. データ転送時の衝突を回避し高速化するために CPU は投機実行などを行う. 一方で半導体メモリの観点から見ると図 1.1 で示したように、SRAM と DRAM との間には約 10<sup>1</sup>倍、DRAM と NAND 型フラッシュメモリとの間には約 10<sup>4</sup>倍のアクセス性能差がある.

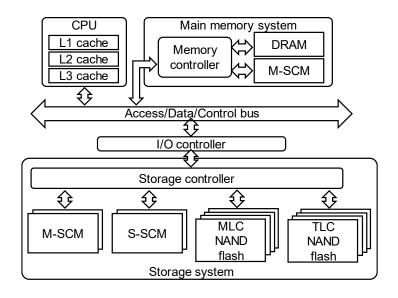

フォンノイマン・ボトルネックとなる DRAM と NAND 型フラッシュメモリとのアクセス性能差を埋めるため、ストレージクラスメモリ(storage class memory, SCM)と呼ばれる不揮発性半導体メモリが研究、開発されてきた[3][4]. SCM は magnetoresistive RAM (MRAM) [5][6], resistive RAM (ReRAM) [7][8][9], phase change RAM (PRAM) [10][11][12]など次世代の不揮

図 2.2 M-SCM および S-SCM を用いた将来のコンピュータアーキテクチャ

発性半導体メモリの総称である.SCM は DRAM より大容量で NAND 型フラッシュメモリよ り高いアクセス性能を持つことを特徴とする. SCM を用いた次世代のコンピュータアーキテ クチャを図 2.2 に示す. SCM はメインメモリシステムおよびストレージシステムにおいて用 いられる. 図 1.1 に示したように SCM はメモリタイプ (memory-type SCM, M-SCM) とスト レージタイプ (storage-type SCM, S-SCM) とに分類できる. M-SCM は DRAM により近い特 性を持つためメインメモリシステムで用いられる.メインメモリシステムでは例えば、DRAM とハイブリッド化し低いアクセス頻度のデータを M-SCM に保存する研究が行われている [13]. またストレージシステムでは M-SCM および S-SCM を用いることを本論文で提案する. M-SCM および S-SCM はフォンノイマン・ボトルネックである DRAM と NAND 型フラッシ ュメモリ間の性能差を埋めるために用いる. さらに NAND 型フラッシュメモリも, NAND 型 フラッシュメモリセル当たりに保存するビット数によって, Single-level cell (SLC, 1 bit/cell), Multiple-level cell (MLC, 2 bit/cell), Triple-level cell (TLC, 3 bit/cell) が存在しそれぞれメモ リ特性が異なる.これらの半導体メモリはその特性に一長一短があるため、高速、大容量、 不揮発なユニバーサルメモリは存在しない、そのためこれらの異種の不揮発性半導体メモリ を複数種用いて構成し、本論文でヘテロジニアスストレージと呼ぶ.

#### 2.3 不揮発性半導体メモリ

本論文で提案するヘテロジニアスストレージを構成する不揮発性半導体メモリである, SCM および NAND 型フラッシュメモリについてその動作およびその特性を述べる.

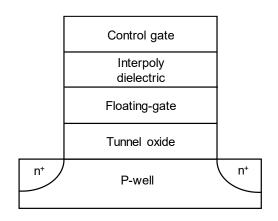

図 2.3 フローティングゲート型 NAND 型フラッシュメモリセル [14]

# 2.3.1 NAND 型フラッシュメモリ

図 2.3 に NAND 型フラッシュメモリセルを示す. P 型半導体基板 (P-well) 上に酸化膜 (tunnel oxide) と制御ゲート (control gate, CG) を構成する MOS トランジスタと比較して、NAND 型フラッシュメモリセルは酸化膜と制御ゲートとの間に浮遊ゲート (floating gate, FG) 層を構成する点が異なる[14]. 浮遊ゲートは絶縁膜により電気的に隔離されており、電源を与えることなく浮遊ゲート内に保存された電子を保持することができるため不揮発である. NAND 型フラッシュメモリセルの書き込みおよび読み出しは、制御ゲートと P 型半導体基板間に電圧を加えることで行う. データ書き込み時は P 型半導体基板に 0V および制御ゲートに 20V を加えることで,Fowler-Nordheim トンネリングにより電子は NAND 型フラッシュメモリセルの浮遊ゲートに注入される. このとき論理的な"0"状態にしきい値電圧が上昇する[15]. 一方でデータ消去時,トンネル電圧を書き込み時とは反対に P 型半導体基板に 20V および制御ゲートに 0V を加えることで,電子を浮遊ゲートから排出する. これはセルのしきい値電圧を低下させ、論理的な"1"状態にする. つまりデータの書き込み/消去 (write/erase) を行うと、NAND 型フラッシュメモリセルの P 型半導体基板と酸化膜との間で電子の移動が起こる. 何度もデータの書き込み/消去を行うと酸化膜が劣化するため NAND 型フラッシュメモリの書き換え回数 (Write/erase cycle) は制限されている.

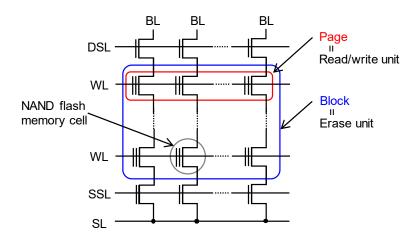

図 2.4 に NAND 型フラッシュメモリの回路を示す[16]. NAND 型フラッシュメモリの回路は、ビットライン(bit-line, BL)とワードライン(word-line, WL)の交点に NAND 型フラッシュメモリセルが格子状に並ぶ。ビットラインはそれぞれの NAND 型フラッシュメモリセルのソースとドレインに接続される。ワードラインはまた、それぞれの NAND 型フラッシュメモリセルの制御ゲートに接続される。ワードラインおよびビットラインの電圧を制御するこ

図 2.4 NAND 型フラッシュメモリ回路 [16]

とで、NAND型フラッシュメモリセルの書き込み、読み出し、消去を行う。NAND型フラッ シュメモリ回路にはページおよびブロックの単位がある、ページは同一のワードラインを共 有する NAND 型フラッシュメモリセルの集まりで、ワードライン電圧を制御することで同時 に読み出し、書き込みができる. ブロックは同一のビットラインを共有する NAND 型フラッ シュメモリセルの集まりである.NAND 型フラッシュメモリセルのデータ消去は P 型半導体 基板に 20V 加えることで達成されるため、同一のビットラインを共有する複数のページから なるブロック単位でのみ消去できる.このように NAND 型フラッシュメモリは読み出し・書 き込み動作はページ単位で、消去動作はブロック単位で行われる. NAND 型フラッシュメモ リセルの書き込み・消去単位の非対称性はチップ面積を削減しコスト低減する目的であり、 現在ではさまざまな用途に NAND 型フラッシュメモリが用いられている.

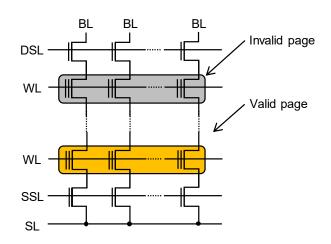

NAND 型フラッシュメモリの書き込み・消去単位の非対称性のため、同一ページ内で上書 き動作ができない[17][18][19]. そのため NAND 型フラッシュメモリのページの状態を有効 (valid),空(free),無効(invalid)と表しコントローラが管理する.有効ページは現存のデ ータを保存したページである. 空のページはデータが無い状態であり, データを書き込むこ とができる.無効ページはすでにデータが書き込まれているが,データは古いあるいは無効 な状態である、書き込み・消去単位の非対称性により、ブロック全体を消去しなければ無効 ページにデータを書き込むことができない. NAND 型フラッシュメモリに上書きするとき, 古いページのデータを読み出し、新しいデータと統合した後、同じあるいは別のブロックの 空きページに書き込まれる(図 2.5). その後古いページを無効化し,ブロックを消去する準 備を行う. NAND 型フラッシュメモリのコントローラのフラッシュトランスレーションレイ

図 2.5 NAND 型フラッシュメモリのページ管理

ヤ (flash translation layer, FTL) の機能の一つは、これらの複雑なページの状態を管理することである.

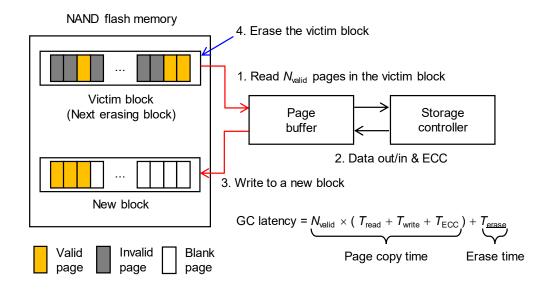

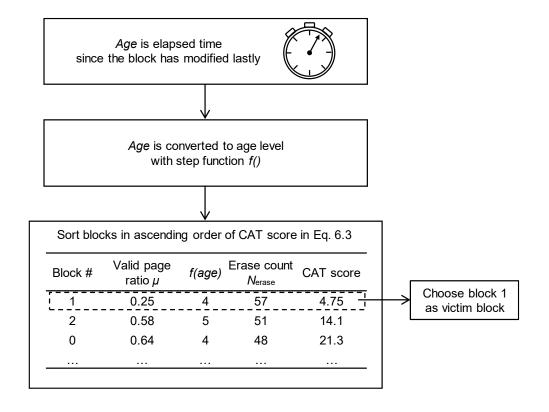

ページの上書きによって無効ページが増えると、書き込みに使える空ページの数が減少す る. そのため無効ページを消去し, 空ページをつくるガベージコレクション (garbage collection, GC) を行う必要がある. 実際の NAND 型フラッシュメモリでは, 空ページの数があらかじめ 決めたしきい値より少なくなると GC が行われる. 図 2.6 に GC 動作を示す. 初めに消去予定 のブロックの有効ページをコントローラに読み出しエラー訂正を行う. 消去予定ブロック内 の有効ページ数を  $N_{\text{valid}}$  とする.次にエラー訂正を行った有効ページのデータを、消去予定の ブロックとは異なるブロックに書き込む. 最後に消去予定のブロックを消去する. これらの GC動作に要する時間は、有効ページを消去予定のブロックから別のブロックにコピーする時 間と,ブロックを消去する時間との和となる.消去するブロックの有効ページ数が多い場合, GC に要する時間は 100 msec を超える[20][21]. また消去するブロックの有効ページ数が多い と write amplification が起きる[22]. Write amplification とは NAND 型フラッシュメモリ内部の 上書きや GC 動作によって,ホストからの書き込みと比較して NAND 型フラッシュメモリへ の書き込み量が増える現象である. Write amplification が起きると NAND 型フラッシュメモリ の書き換え回数が増加し、制限のある NAND 型フラッシュメモリの許容書き換え回数を圧迫 する. このように GC 動作は NAND 型フラッシュメモリの性能を低下させるボトルネックと なる.

図 2.6 NAND 型フラッシュメモリのガベージコレクション動作 [20]

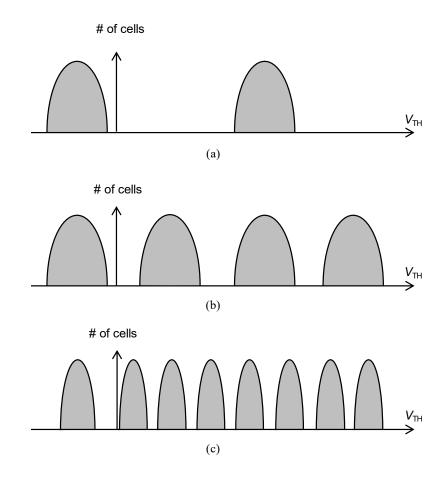

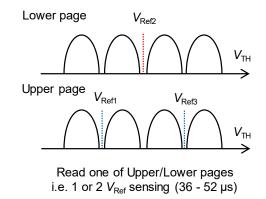

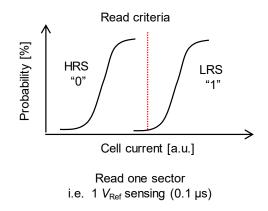

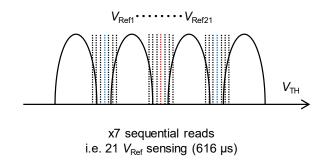

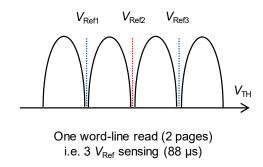

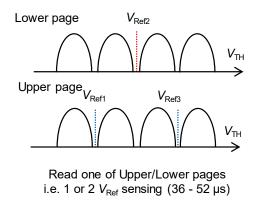

NAND 型フラッシュメモリは 2 次元のスケーリング[23], 多値化技術[24][25]および 3 次元 積層技術[26]によって大容量化しビットコストを低下させている. 多値化技術は NAND 型フ ラッシュメモリのセル当たりに 2 bit 以上を保存する.初期の NAND 型フラッシュメモリは、 NAND 型フラッシュメモリのセル当たりに 1 bit を保存する Single-level cell (SLC, 1 bit/cell) であった. 次に NAND 型フラッシュメモリのセル当たりに 2 bit を保存する Multiple-level cell (MLC, 2 bit/cell) が開発され、現在でも多くのストレージ製品に用いられている. 近年では NAND型フラッシュメモリのセル当たりに 3 bit を保存する Triple-level cell (TLC, 3 bit/cell) が大容量を目的とする製品に用いられる。また NAND 型フラッシュメモリのセル当たりに 4 bit を保存する Quadruple-level cell (QLC, 4 bit/cell) 製品の開発も予定されている[27]. 図 2.7 に SLC、MLC および TLC NAND 型フラッシュメモリのしきい値 ( $V_{TH}$ ) 分布を示す. SLC NAND 型フラッシュメモリは消去状態"1"および書き込み状態"0"と、2(= 2¹) 状態のしきい 値電圧を持つ. NAND 型フラッシュメモリセルの浮遊ゲートに注入する電子の量を制御する ことで、MLC NAND型フラッシュメモリは $4 (= 2^2)$  状態のしきい値電圧を持つ. 同様にTLCNAND 型フラッシュメモリは  $8 (= 2^3)$  状態のしきい値電圧を持つ. そのため, MLC および TLC NAND 型フラッシュメモリは SLC NAND 型フラッシュメモリと比較して、それぞれ 2 倍,3倍のビット密度を持つ.しかし図2.7から明らかなように,多値化技術を用いたMLC および TLC NAND 型フラッシュメモリは SLC NAND 型フラッシュメモリと比較してしきい 値電圧の間隔が狭くなる. そのためしきい値分布を詳細に制御するための時間がかかり、MLC

図 2.7 多値化 NAND 型フラッシュメモリのしきい値分布. (a) SLC, (b) MLC, (c) TLC NAND 型フラッシュメモリ

および TLC NAND 型フラッシュメモリは SLC NAND 型フラッシュメモリと比較して読み出し、書き込み、消去時間が長くなる。NAND 型フラッシュメモリは時間経過などにより、トンネル酸化膜中のトラップサイトを経由して電子のトンネリングが発生し、さらにトンネル酸化膜中にトラップされた電子がデトラップされる。また隣接セルに書き込む際、電子が誤って注入されるなどしてビット反転が起き、異なるしきい値電圧に変化するエラーが起きる。特に TLC NAND 型フラッシュメモリはしきい値電圧の間隔が狭いためビット反転が起きやすい。

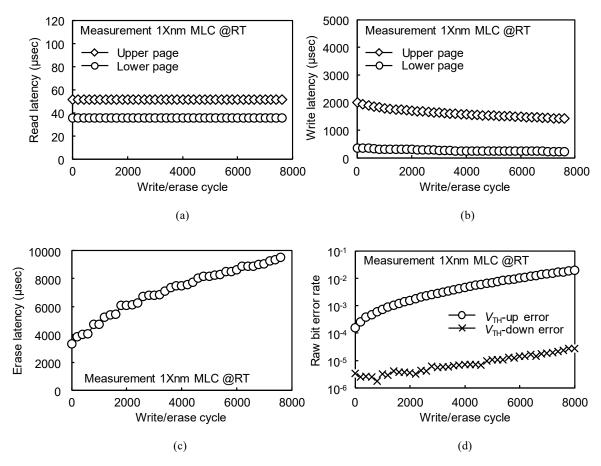

図 2.8, 図 2.9 に MLC および TLC NAND 型フラッシュメモリを実測した (a) ページ読み出し時間, (b) ページ書き込み時間, (c) ブロック消去時間, (d) ビットエラーレート (bit error rate, BER) を示す[28]. NAND 型フラッシュメモリの書き換え (W/E cycle) に対して (a) ページ読み出し時間はほぼ一定である. しかし NAND 型フラッシュメモリの書き換えによってトンネル酸化膜に捕獲された電子が増加する[29]. その結果しきい値電圧が上昇するため,

図 2.8 MLC NAND 型フラッシュメモリの(a) ページ読み出し時間,(b) ページ書き込み時間, (c) ブロック消去時間, (d) Bit error rate [28]

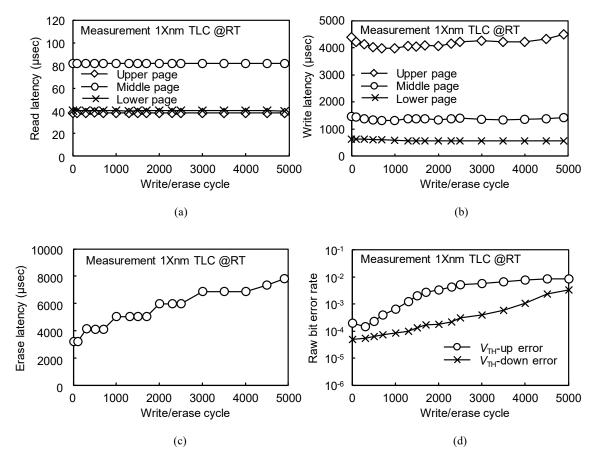

W/E cycle の増加によって(b)ページ書き込み時間は減少し、(c)ブロック消去時間は増加す る. また W/E cycle の増加によってトンネル酸化膜が劣化し(d) BER が増加する. 次に MLC および TLC NAND 型フラッシュメモリの動作時間を比較する. TLC NAND 型フラッシュメ モリは MLC NAND 型フラッシュメモリと比較してしきい値状態の数が多いため、しきい値 分布を詳細に制御するための時間がかかり、TLC NAND 型フラッシュメモリは MLC NAND 型フラッシュメモリと比較して(a)ページ読み出し,(b)ページ書き込み,(c)ブロック消 去時間が長くなる. また (d) BER のようにしきい値が上がるエラー ( $V_{TH}$ -up error) としきい 値が下がるエラー ( $V_{TH}$ -down error) を区別して計測した. 特に TLC NAND 型フラッシュメモ リはしきい値分布が狭いため、書き換えによってしきい値が下がるエラーが増加する. NAND 型フラッシュメモリはメモリコストが市場を拡大する推進力であるため、多値化技術による 欠点があるにも関わらずセル当たりにより多くのビットが保存される.

図 2.9 TLC NAND 型フラッシュメモリの (a) ページ読み出し時間, (b) ページ書き込み時間, (c) ブロック消去時間, (d) Bit error rate [28]

#### 2.3.2 ストレージクラスメモリ(SCM)

図 1.1 に示したメモリおよびストレージ階層において,ストレージクラスメモリ (storage class memory, SCM) は DRAM と NAND 型フラッシュメモリとの間に位置する. SCM は DRAM と NAND 型フラッシュメモリとの間の特性を有する不揮発性半導体メモリのことを 指す総称である. 磁気抵抗型メモリ (magnetoresistive RAM, MRAM) [5][6],抵抗変化型メモリ (resistive RAM, ReRAM) [7][8][9],相変化メモリ (phase change RAM, PRAM) [10][11][12] が SCM の候補である. 以下に SCM の動作を示す.

図 2.10 にスピン注入型磁気抵抗型メモリ(spin transfer torque MRAM, STT-MRAM)の書き 込み原理を示す。STT-MRAM は強磁性体に挟まれた絶縁層から構成され、これを磁気トンネ ル接合(magnetic tunnel junction, MTJ)素子と呼ぶ。強磁性体に電圧を加えることで free layer の磁化が reference layer の磁化と同一極性あるいは反極性に変化しトンネル電流が流れる。 Free layer の磁化が reference layer の磁化と同一極性のとき高抵抗状態で論理的な"1"となり、

図 2.10 磁気抵抗型メモリ (MRAM) の動作 [5]

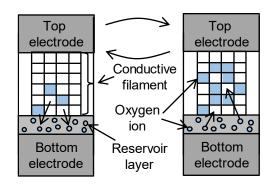

図 2.11 抵抗変化型メモリ (ReRAM) の動作 [9]

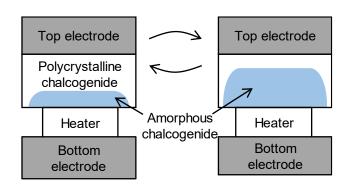

図 2.12 相変化メモリ (PRAM) の動作 [11]

反極性のとき低抵抗状態となり論理的な"0"を表す.

図 2.11 に ReRAM の書き込み原理を示す. ReRAM は一般に遷移金属酸化物層と上下の電極 (top/bottom electrode) から構成される. 図 2.11 に示す ReRAM の遷移金属酸化物層は、導電性フィラメント (conductive filament) を形成する層と酸素イオンを貯める層 (reservoir layer)

を持つ[7]. 下部電極に電圧を加えると酸素イオンが下部の reservoir layer へ移動し、導電性フィラメントには酸素欠陥が発生する. このとき導電性フィラメントは電流が流れやすい低抵抗状態 ("1") となる. また上部電極に電圧を加えると reservoir layer から導電性フィラメントへ酸素イオンが拡散する. 酸素イオンによって導電性フィラメント内の酸素欠陥が減少し、電流が流れにくい高抵抗状態 ("0") となる.

図 2.12 に PRAM の書き込み原理を示す. PRAM はカルコゲナイド材料を上下電極で挟んだ構成である. 電極に電圧を加え大電流が流れると, ジュール熱によりカルコゲナイド材料の温度が上昇し結晶状態となる. このとき電流が流れやすい低抵抗状態("1")と呼ぶ. また高電圧を加えると大電流が流れカルコゲナイド材料は融解する. 続いて電圧を下げるとカルコゲナイド材料の温度は急激に低下しアモルファス状態となる. このとき電流が流れにくい高抵抗状態("0")となる. このように PRAM はカルコゲナイド材料を結晶化および融解することにより状態を変化させるため, MRAM, ReRAM と比較して消費電力が大きく並列化の点で不利である.

これら将来の不揮発性半導体メモリである SCM は、NAND 型フラッシュメモリより短い 読み出し・書き込み時間を持ち、DRAM より大容量であるため、DRAM と NAND 型フラッシュメモリ間の性能差を埋めるメモリとして期待されている。 SCM は NAND 型フラッシュメモリと同様に不揮発性である。 さらに NAND 型フラッシュメモリの最小アクセス単位がページであるのに対し、SCM はバイトアクセスが可能である。また、NAND 型フラッシュメモリがアクセス単位の非対称性により GC 動作が必要であるのに対し、ストレージで用いる SCM は HDD と同じくセクタ(ブロックともいう、512 Byte)で行うため消去動作は不要で同ーセクタで上書き可能である。しかしほぼ無制限の書き換え回数を許容する DRAM と比較して、SCM は上記で述べた動作原理により書き換え回数に制限があるため、完全なユニバーサルメモリではない。

SCM はそれぞれ書き込み原理が異なるため、MRAM、ReRAM、PRAM は異なる特性を持つ。 SCM のアクセス速度と容量に応じて、SCM はメモリタイプ SCM (memory-type SCM、M-SCM) とストレージタイプ SCM (storage-type SCM、S-SCM) に分類できる[30]。本研究では、MRAM は DRAM 並みに高速化が実現可能で高い書き換え耐久性を持つため M-SCM として分類する。一方で ReRAM や PRAM は、SLC NAND 型フラッシュメモリと同等の大容量を実現し低コストとなる可能性があるため S-SCM に分類する。表 2.1 および表 2.2 に本研究で仮定した不揮発性半導体メモリの特性をまとめる[31]。M-SCM は S-SCM と比較して約 10<sup>1</sup>-

| Memory device               | SCM                  | MLC NAND flash                          | TLC NAND flash                                                |

|-----------------------------|----------------------|-----------------------------------------|---------------------------------------------------------------|

| Read latency                | 表2.2に示す              | 52 μsec/page (U)<br>36 μsec/page (L)    | 80 μsec/page (U)<br>100 μsec/page (M)<br>80 μsec/page (L)     |

| Write latency               |                      | 2000 μsec/page (U)<br>370 μsec/page (L) | 4400 μsec/page (U)<br>1500 μsec/page (M)<br>640 μsec/page (L) |

| Erase latency               | Not required         | 3300 µsec/block                         | 3200 µsec/block                                               |

| I/O frequency               | 1066 MHz             | 400 MHz                                 |                                                               |

| V <sub>DD</sub> (Core, I/O) | 1.8 V, 1.2 V         | 3.3 V, 1.8 V                            |                                                               |

| I (read, write, erase)      | 20 mA, 40 mA, -      | 45 mA, 45 mA, 45 mA                     |                                                               |

| Minimum access unit         | Sector<br>(512 Byte) | Page<br>(16 KByte)                      | Block<br>(4.03 MByte)                                         |

| Acceptable endurance        | 表2.2に示す              | $10^{4}$                                | $10^{3}$                                                      |

| Bit cost                    |                      | 1                                       | 2/3                                                           |

表 2.1 不揮発性半導体メモリの特性 [31]

U: Upper page, M: Middle page, L: Lower page of NAND flash

6

| SCM<br>scenario | 1<br>(M-SCM) | 2<br>(S-SCM) | 3<br>(S-SCM) |

|-----------------|--------------|--------------|--------------|

| Read latency    | 0.1 μsec     | 1 μsec       | 10 μsec      |

| Write latency   | 0.1 μsec     | 1 μsec       | 10 μsec      |

| Acceptable      | 1012         | $10^{8}$     | $10^{6}$     |

10

表 2.2 ストレージクラスメモリ (SCM) の特性 [31]

10<sup>2</sup> 倍短い読み出し・書き込み時間を持ち, M-SCM は S-SCM より約 10<sup>6</sup>-10<sup>2</sup> 倍高い書き換え 耐久性を持つと仮定した. DRAM のビットコストが MLC NAND 型フラッシュメモリの約 12 倍であることから[32], M-SCM および S-SCM のビットコストはそれぞれ MLC NAND 型フラ ッシュメモリの 10 倍, 6 倍, 4 倍と仮定した[31]. M-SCM のアクセス時間は DRAM 並みに 短いが、その書き込みエネルギーは DRAM より高い. 一方で、S-SCM の書き換え回数は MLC NAND 型フラッシュメモリより約 10<sup>2-</sup>10<sup>4</sup> 倍多い. S-SCM は NAND 型フラッシュメモリより 高コストだが、M-SCM と比較すると費用対効果が高い.

#### 2.4 SCM および NAND 型フラッシュメモリを用いたストレージ

Bit cost

ストレージクラスメモリ (SCM) の出現により、図 2.2 のように次世代のコンピュータア

ーキテクチャが大きく変わろうとしている. 現在,メインメモリには DRAM, 二次記憶(ストレージ)には NAND 型フラッシュメモリあるいは HDD が主に用いられている. SCM はメインメモリシステムおよびストレージシステムの性能を向上させると期待される. メインメモリシステムでは、SCM はシステムの消費エネルギーを削減するのに役立つ. SRAM のリーク電力を無くすために、MRAM と SRAM をハイブリッド化した L2 キャッシュ[33]、MRAM と DRAM をハイブリッド化した last level cache (LLC) が提案されている[34]. さらに、PRAM および DRAM をハイブリッド化したメインメモリは、PDRAM と呼ばれ、待機電力を削減する[35]. また、SCM に対応した Linux ベースのファイルシステムとして、Diret Access(DAX)[36]がある. SCM から読み出したデータをカーネル空間に DMA 転送し、カーネル空間から直接 CPU へデータ転送する. ファイルシステム経由だが、カーネル空間からユーザ空間へコピーしない点を直接アクセスできるという. また、バイト単位でも SCM ヘアクセス可能である.

# 2.4.1 SCM および NAND 型フラッシュメモリを用いたハイブリッドストレージ

一方で、ストレージ性能を向上させるため、SCM と NAND 型フラッシュメモリを用いたハイブリッドストレージシステムの研究が行われている。SCM は小さいサイズのデータを保存し、NAND 型フラッシュメモリの write amplification を減少する。例えばデータの種類によって書き込む不揮発性半導体メモリを変える。NAND 型フラッシュメモリがユーザデータだけを保存するのに対し、SCM はメタデータ、論物変換テーブル、ECC のパリティビットを保存するのに用いられる。たとえば Sun ら[37]は PRAM と NAND 型フラッシュメモリでデータを分けるハイブリッドストレージを提案している。その中で、PRAM は頻繁に更新されるログデータを保存するために用いられ、この結果、NAND 型フラッシュメモリの GC オーバーヘッドが減少する。Fujii ら[21]は ReRAM と NAND 型フラッシュメモリを用いたハイブリッドストレージにおいて、ホットかつランダムなデータを ReRAM に保存することを提案した。この結果 NAND 型フラッシュメモリのみを用いたストレージと比較して、書き込みだけを行うアプリケーションに対して 10 倍以上性能を向上させることを示した。

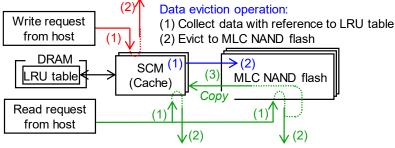

また、SCM は不揮発性キャッシュあるいは小容量のストレージとして用いられる. SCM と NAND 型フラッシュメモリとを階層化して構成したハイブリッドストレージは、NAND 型フラッシュメモリを用いたストレージの性能を向上させる有望な手法である. いくつかのハイブリッドストレージの構成およびデータマネジメントアルゴリズムが提案されている [38][39][40]. これらのアルゴリズムでは、頻繁にアクセスされるホットデータ (hot data) は

#### Write operation:

- (1) Write to SCM and update LRU table

- (2) Return "write complete" to host

#### Read operation:

- (1) Read from SCM or MLC NAND flash

- (2) Return "read complete" to host

- (3) Copy data to SCM if read from MLC NAND flash

図 2.13 不揮発性半導体メモリ向けライトバックキャッシュ (Non-Volatile Memory Write-Back, NV-WB) アルゴリズム [39]

SCM に保存される、従来の揮発性半導体メモリを用いたキャッシュアルゴリズムでは、キャ ッシュミスおよびデータの一貫性を保証するために、ホットデータはキャッシュメモリおよ び不揮発性ストレージの両方に保存されている。しかし、以下で説明するデータマネジメン トアルゴリズムは SCM の不揮発性のために、電源遮断時にデータを退避させる必要がなく、 SCM あるいは NAND 型フラッシュメモリだけに保存することもできる.

図 2.13 は SCM と NAND 型フラッシュメモリを用いたハイブリッドストレージに用いる, 不揮発性半導体メモリ向けライトバック (Non-Volatile Memory Write-Back, NV-WB) キャッ シュデータマネジメントアルゴリズムを示す[39][40]. DRAM がその揮発性のために定期的な データフラッシュ動作を必要とする.しかし SCM の不揮発性のために,NV-WB キャッシュ は定期的なデータフラッシュ動作が不要である.加えて揮発性の DRAM と異なり、NV-WB キャッシュは突然の電源障害に対して安全である. NV-WB キャッシュアルゴリズムでは、す べてのデータは初めにキャッシュメモリとしての SCM に書き込まれる.NV-WB キャッシュ アルゴリズムは、すべてのデータを SCM に書き込むため高い性能を示す. したがって高速な SCM がハイブリッドストレージの応答時間を短縮する. SCM がデータでいっぱいになると, least recently used (LRU) 順に SCM 内のデータを NAND 型フラッシュメモリに evict する. Evict とは、上位のメモリから下位のメモリへ不要なデータを移動することである. LRU リス トは、一番最近にアクセスされた (most recently used, MRU) データから、最も古くアクセス されたデータ(LRU)データの順番を記録する. 本研究では SCM 容量が残り 20%になると

evict 動作を発動することとした[39]. SCM からデータを読み出すとき, SCM と NAND 型フ ラッシュメモリとの間でデータの移動は発生しない. 一方 NAND 型フラッシュメモリからデ ータを読み出すとき、そのデータは近い将来再びアクセスされる可能性があるため SCM ヘコ ピーされクリーンデータ (clean data) となる. これに対し, ダーティデータ (dirty data) は SCM への上書きで発生する. SCM と NAND 型フラッシュメモリとの間でデータの一貫性が 保たれていれば、そのデータはクリーンであるという. そうでないとき、そのデータはダー ティであるという. クリーンデータが SCM から NAND 型フラッシュメモリに evict されると き,そのデータはすでに NAND 型フラッシュメモリに保存されているため書き込み動作は不 要である. しかし, ダーティデータを evict するとき, SCM のデータを NAND 型フラッシュ メモリに書き込む必要がある.このようなデータマネジメントにより、頻繁にアクセスされ るホットデータ,めったにアクセスされないコールドデータは SCM および NAND 型フラッ シュメモリにそれぞれ保存される. NV-WB キャッシュの一つの問題は, 頻繁にアクセスされ ないコールドデータおよびデータサイズの大きいシーケンシャルデータもすべて初めに SCM に保存されるため、ハイブリッドストレージの性能を低下させることである. また SCM 容量が小さい場合に読み出しの多いアプリケーションに対して, SCM と NAND 型フラッシ ュメモリ間でデータが循環する問題がある[40]. SCM でキャッシュヒットする前にデータが SCM から NAND 型フラッシュメモリヘ evicts され, さらに NAND 型フラッシュメモリから 読み出しが頻繁に発生する場合データが循環する.

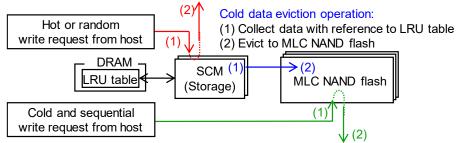

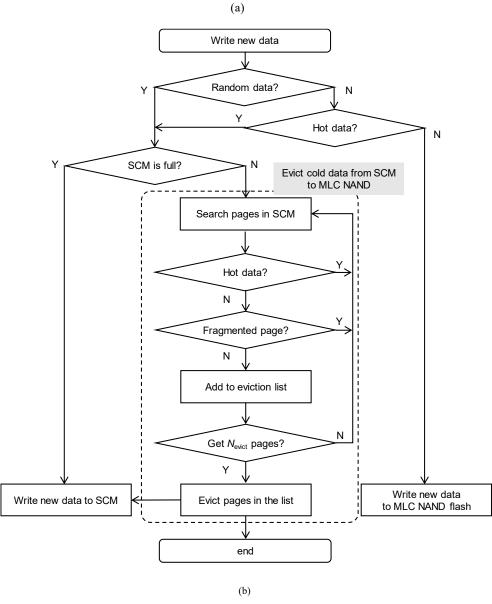

ホットあるいはランダムデータとコールドかつシーケンシャルデータを分離するため、コールドデータエビクション(Cold Data Eviction、CDE)アルゴリズムが提案された[38]。NV-WB キャッシュではたくさんのコールド・シーケンシャルデータが SCM に書き込まれると、頻繁にアクセスされるホットデータが NAND型フラッシュメモリに evict され SCM でのヒット率が低下する。それに加えて、ランダムデータは NAND型フラッシュメモリのデータ断片化を起こし、write amplification を発生させる。したがって、CDE アルゴリズムでは、SCM はホットあるいはランダムデータを保存し、NAND型フラッシュメモリはコールドかつシーケンシャルデータを保存する。SCM と NAND型フラッシュメモリで重複したデータを保存しないため、SCM はストレージとして用いられる。図 2.14(a)に示すように、ホストからのホットあるいはランダムデータは SCM に書き込まれ、コールドかつシーケンシャルデータは直接 NAND型フラッシュメモリに書き込まれる。図 2.14(b)に CDE アルゴリズムの詳細を示す。固定したサイズのLRU リストを用い、データのアクセス履歴を記録する。LRU に存在するデータはホットデータと判断される。書き込みリクエストのサイズによって、ランダムあ

#### Hot and random write operation:

- (1) Write to SCM and update LRU table

- (2) Return "write complete" to host

Cold and sequential write operation:

- (1) Write to MLC NAND flash

- (2) Return "write complete" to host

図 2.14 コールドデータエビクション (Cold Data Eviction, CDE) アルゴリズムの (a) 概要, (b) フローチャート [38]

るいはシーケンシャルと判断される.本研究で定義した NAND 型フラッシュメモリのページサイズ (16 KByte) と比較して、以下の図 2.16 で示すアプリケーション分類と同様に、書き込みデータのサイズが NAND型フラッシュメモリのページサイズの半分より小さいとランダムであると判断される. SCM がデータでいっぱいになると、LRU リストを参照して、コールドかつシーケンシャルデータは SCM から NAND型フラッシュメモリに evict される. ホストからのリクエストが読み出しの場合、データが保存されたメモリから読み出され、メモリ間のデータの移動は発生しない. したがって、CDE アルゴリズムは書き込みの多いアプリケーションに適している[41].

### 2.4.2 MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレージ

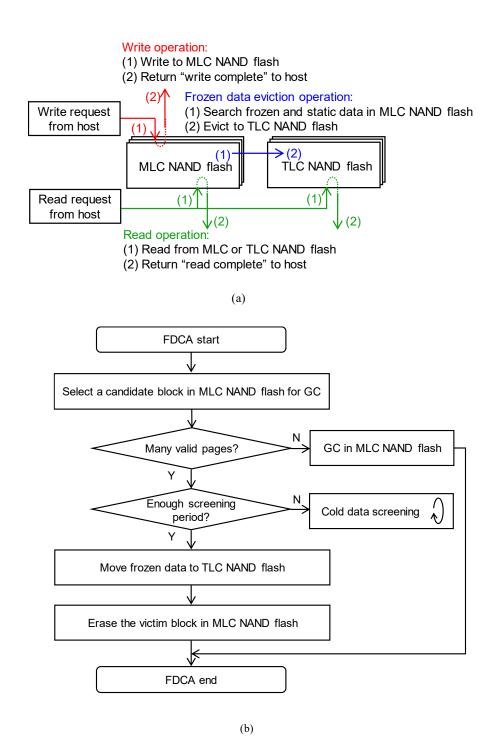

さらにまた, MLC NAND 型フラッシュメモリおよび TLC NAND 型フラッシュメモリを用 いたハイブリッドストレージおよびそのデータマネジメントアルゴリズムが提案されている [42]. 参考文献[43][44]によると, 2DTLCNAND型フラッシュメモリはセル間干渉を削減する ため、その書き込み単位は複数ページをまとめたブロックである.一方で、SLC および MLC NAND 型フラッシュメモリの書き込み単位はページである. つまり NAND 型フラッシュメモ リの 1 ページを上書きするとき, SLC および MLC NAND 型フラッシュメモリは古いデータ を持つページを読み出し、新しいデータと統合して別のページに書き込む. しかし TLC NAND 型フラッシュメモリの1ページを上書きするとき、古いデータを持つページを含む1ブロッ クを読み出し新しいデータと統合して、上書きの必要のないページも別のブロックに書き込 む必要がある. このように書き込み単位の大きい TLC NAND 型フラッシュメモリは SLC お よび MLC NAND 型フラッシュメモリと比較して write amplification が多いため, TLC NAND 型フラッシュメモリの性能は低下し書き換え回数が圧迫される. 従来, SRAM が書き込みバ ッファとしてデータを保存し、TLC NAND型フラッシュメモリに書き込まれるまで待つ[43]. しかし、第1章で述べたように SRAM は高速だが高価で小容量である. MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレージにおいて, MLC NAND 型フラ ッシュメモリは低コストと大容量をバランスした TLC NAND 型フラッシュメモリの書き込 みバッファを実現する. TLC NAND 型フラッシュメモリへのアクセスを削減するため, 図 2.15 (a) に示すラウンドロビン・フローズンデータコレクションアルゴリズム (Round-Robin Frozen Data Collection Algorithm, RR-FDCA) を用いて、TLC NAND 型フラッシュメモリはほ とんど上書きされないフローズンデータを保存する. RR-FDCA においてホストからのすべて の書き込みリクエストは、書き込みバッファとしての MLC NAND 型フラッシュメモリに書 き込まれる. フローズンデータは MLC NAND 型フラッシュメモリの GC 中に、MLC NAND

図 2.15 ラウンドロビン・フローズンデータコレクションアルゴリズム (Round-Robin Frozen Data Collection Algorithm, RR-FDCA) の (a) 概要, (b) フローチャート [38]

型フラッシュメモリから TLC NAND 型フラッシュメモリにコピーされる. 図 2.15 (b) にア ルゴリズムの詳細を示す. フローズンデータの収集は, MLC NAND 型フラッシュメモリの GC 動作中に行われる. 消去するブロックは、NAND 型フラッシュメモリで初めに書き込まれた 最も古いブロックがラウンドロビン方式で選択される. その結果, NAND 型フラッシュのウ

エアレベリングが実行される. NAND 型フラッシュメモリのブロックが GC 動作で消去され るとき、もしブロック内のページが上書きされていれば、有効ページは無効ページに代わる. このため RR-FDCA アルゴリズムでは消去するブロックの有効ページは、MLC NAND 型フラ ッシュメモリの GC 動作が一巡する間に上書きされなかったフローズンデータであると考え る. MLC NAND 型フラッシュメモリのよりフローズンなデータを収集するためブロックの古 さを示すカウンタを用いる. MLC NAND 型フラッシュメモリのより大きなカウントを持つブ ロックは、GC 中に消去するブロックとして選択される. GC 対象として選択した MLC NAND 型フラッシュメモリブロック内の有効ページであるフローズンデータを TLC NAND 型フラ ッシュメモリにコピーする. その後, MLC NAND 型フラッシュメモリのブロックを消去する. RR-FDCA により MLC NAND 型フラッシュメモリは TLC NAND 型フラッシュメモリに evict することで、フローズンデータを保存することから解放される. その結果、MLC NAND型フ ラッシュメモリはホットデータとコールドデータを混在して保存するブロックが減少し、 MLC NAND 型フラッシュメモリの GC 時にコピーすべき有効ページ数が減少する. したがっ て,MLC NAND 型フラッシュメモリのみを用いたストレージと比較して,MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレージは, TLC NAND 型フラッシュメ モリは自身の書き換え回数を小さく保ったまま, MLC NAND 型フラッシュメモリの寿命を延 ばす. RR-FDCA のアルゴリズムを用いると, TLC NAND 型フラッシュメモリはフローズン データ, MLC NAND 型フラッシュメモリはホットあるいはやや頻繁にアクセスされるワーム (warm) データを保存する. さらに, TLC NAND 型フラッシュメモリはめったに上書きされ ないため、書き換え回数は小さく保たれる. MLC および TLC NAND 型フラッシュメモリを 用いたハイブリッドストレージは、MLC NAND 型フラッシュメモリのみを用いたストレージ と比較して高い性能を達成する. しかし SCM を用いたハイブリッドストレージと比較する と、その性能は TLC NAND 型フラッシュメモリの低いアクセス性能で制限される.

#### 2.5 次世代コンピュータアーキテクチャにおけるストレージの課題

第2.4 節で説明した SCM, MLC NAND 型フラッシュメモリ, TLC NAND 型フラッシュメモリを用いたハイブリッドストレージは,上位の高速な不揮発性半導体メモリにアクセスの多いホットあるいはワームデータを保存し,下位の低速な不揮発性半導体メモリにアクセスの少ないコールドあるいはフローズンデータを保存する.表 2.3 に,第2.4 節で述べたストレージの利点および問題点を示す[41]. SCM と MLC NAND 型フラッシュメモリを用いたハイブリッドストレージは,頻繁にアクセスされるデータを SCM へ書き込むことで高性能になる. NV-WB キャッシュアルゴリズムを用いる場合[38][39],すべてのデータは初めに高速な

· Limited performance

improvement

| Storage<br>architecture   | Data management algorithm | Objective                                              | Pros                                                           | Cons                                            |

|---------------------------|---------------------------|--------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|

| SCM and<br>MLC NAND flash | NV-WB cache [38, 39]      | SCM accelerates performance as simple write-back cache | <ul> <li>Fast write latency than<br/>MLC NAND flash</li> </ul> | Cost increase by SCM     Application dependent  |

|                           |                           | CDE [37]                                               | Reduce cold or sequential data access to SCM                   | Increase performance of<br>write-intensive apps |

MLC works as write buffer of

TLC NAND flash

NAND flash

· MLC NAND flash

endurance improvement

MLC and

TLC NAND flash

RR-FDCA

[40]

表 2.3 SCM および NAND 型フラッシュメモリを用いたストレージの利点と問題点 [41]

SCM に書き込むため, ホストへの応答速度 (レイテンシ) が速くなる. また CDE アルゴリズ ム[37]では、ホストからのホットあるいはランダムデータを選択して SCM に書き込むため、 コールドかつシーケンシャルデータを SCM に書き込む必要がない. しかし CDE アルゴリズ ムは読み出し動作による不揮発性半導体メモリ間のデータ移動が生じないため, NV-WB キャ ッシュアルゴリズムと比較して書き込みの多いアプリケーションの性能を向上させる.これ らの SCM と MLC NAND 型フラッシュメモリを用いたハイブリッドストレージは、ホット・ ランダムなデータを SCM で処理するため MLC NAND 型フラッシュメモリの書き換え回数が 削減し、MLC NAND型フラッシュメモリを長寿命化することができる. 一方 SCM を用いる ことによる問題は、SCM の高いビットコストである.MLC NAND 型フラッシュメモリ容量 に対して M-SCM を 10%追加する場合,総ストレージコストは約2倍となる.また,SCM お よび MLC NAND 型フラッシュメモリ間での複雑なデータ管理が必要となる. MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレージは, SCM を用いる場合と比 較して低コストで実現できる.しかし SCM と比較して MLC および TLC NAND 型フラッシ ュメモリの性能は劣るため、ストレージ性能の向上は制限される. また、これらの複数種の 不揮発性半導体メモリを用いたストレージは、ストレージアプリケーションの特性に大きく 依存する.

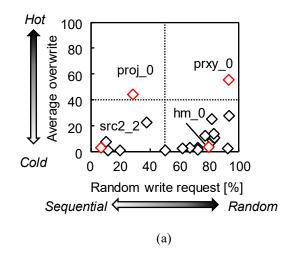

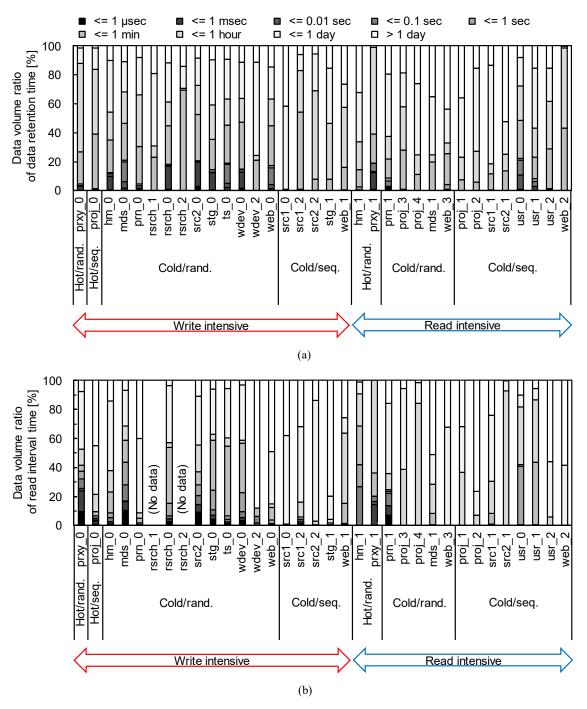

本研究ではストレージアプリケーションとして, Microsoft Research Cambridge の 1 週間の ブロック I/O トレースを用いる[45]. MSR ストレージアプリケーションは, プロキシデータ べースサーバ、プロジェクト用ディレクトリなどから取得した1週間の読み出し・書き込み リクエストを含む.参考文献[39]では、読み出し・書き込み量の多寡、平均データアクセス頻 度, 平均データサイズを用いて, 図 2.16 のようにストレージアプリケーションを 8 分類して いる、第一に、アプリケーションの読み出し・書き込みの多さは、読み出しデータ量および 書き込みデータ量を用いて判断される. 書き込みデータ量が読み出しデータ量より多い場合,

- Average overwrite = Total write data size / user data size

- → Average read frequency = Total read data size / user data size

- Random: data size is 8 KByte (half of NAND flash page size) or less

図 2.16 ストレージアプリケーション[45]の分類. (a) 書き込み多いアプリケーション, (b) 読み出しの多いアプリケーション [39]

そのストレージアプリケーションは書き込みの多い(write-intensive)アプリケーションと定義する[図 2.16 (a) ]. 反対に読み出しデータ量が書き込みデータ量より多い場合, そのストレージアプリケーションは読み出しの多い(read-intensive)アプリケーションと定義する[図 2.16 (b) ]. 第二にストレージアプリケーションの各リクエストは, ホストからの論理アドレス (logical block address, LBA) へのアクセス頻度によって, ホット (hot) またはコールド (cold) に分類する. アプリケーションの論理アドレスが平均して頻繁にアクセスされる場合をホットアプリケーションとし, そうでない場合をコールドアプリケーションとする. 第三に, ストレージアプリケーションの平均アクセスサイズを用いて, ランダムあるいはシーケ

図 2.17 ストレージアプリケーション[45]のアクセス時間間隔の解析. (a) 書き込み時間間隔 (データリテンション時間), (b) 読み出し時間間隔

ンシャルであると判断する. 具体的には、アクセス (読み出しおよび書き込み) リクエスト の平均サイズが NAND 型フラッシュメモリのページサイズの半分である 8 KByte と比較し て、小さい場合をランダム (random) と定義する. 反対に平均アクセスサイズが 8 KByte よ り大きい場合をシーケンシャル(sequential)とする. 一例として, prxy 0 アプリケーション は、書き込みが多くホット・ランダムであると分類される.また、参考文献[46]で解析してい るように、MSR ストレージアプリケーションによりデータアクセスの時間間隔が異なる. 図 2.17 に本研究で用いるストレージアプリケーションのアクセス時間間隔を示す. 先の図 2.16 に分類したホットなアプリケーションほどアクセス時間間隔が短いことがわかる. 特に prxy 0 アプリケーションは 88%のデータが 1 時間以内に上書きされる.

したがって、このように複雑な特性を持つストレージアプリケーションに最適化したスト レージを構築する必要がある. これを実現するために, 本論文において異種の不揮発性半導 体メモリを用いたヘテロジニアスストレージを提案する. ヘテロジニアスストレージの記憶 には第2.3節で説明した新たな不揮発性半導体メモリであるM-SCM, S-SCM, および現在ス トレージシステムで用いられている MLC NAND 型フラッシュメモリおよび TLC NAND 型フ ラッシュメモリを用いる.これらの不揮発性半導体メモリはアクセス時間,書き換え耐久性 (許容書き換え回数),容量,ビットコストなどが異なる.そのため,それぞれの不揮発性半 導体メモリの特性を最大限利用するためのデータマネジメントアルゴリズムやメモリ容量比 を, ストレージアプリケーションに対して最適化する必要がある. また, 各種 SCM および NAND 型フラッシュメモリは動作原理が異なるため、書き換えや読み出しに対するエラー発 生頻度が異なる. エラー訂正符号 (error-correcting code, ECC) を用いて不揮発性半導体メモ リに発生したエラーを訂正するが、ストレージアクセス性能を低下させる. またデータマネ ジメントアルゴリズムを用いることによって, SCM と NAND 型フラッシュメモリのアクセ ス頻度も異なる. さらに SCM の容量が多くなるほど SCM へのアクセス頻度が高まり, NAND 型フラッシュメモリへのアクセス頻度は低減される.ECC によりストレージの信頼性を高め る一方で、ストレージのアクセス性能を低下させないことが必要である。さらにストレージ アプリケーションにより, ストレージを高速化するために必要な SCM 容量が異なる. しかし データセンターで動作するさまざまなストレージアプリケーションに対し、手動で最適な SCM 容量を調整することは不可能である. また SCM は NAND 型フラッシュメモリと比較し て高いビットコストを持つ. ストレージアプリケーションが必要な場合にのみ SCM を用い る, SCM 容量の自律調整が必要である.

#### 2.6 まとめ

本章では不揮発性半導体メモリを用いたストレージの従来研究および問題点について述べた. 初めに SCM の登場により次世代のコンピュータアーキテクチャが変わることを述べた. SCM はメモリシステムおよびストレージシステムで用いられる可能性があり、本論文では SCM と NAND 型フラッシュメモリを用いたストレージシステムの研究を行う. 次に本研究

のストレージシステムの記憶として用いる SCM と NAND 型フラッシュメモリの動作を述べ た. SCM はその特性によってメモリタイプおよびストレージタイプに分類でき,一方で NAND 型フラッシュメモリはセル当たりに保存するビット数によって SLC, MLC, TLC に分 類できることを示した. これらの不揮発性半導体メモリはアクセス時間, 書き換え耐久性な どがそれぞれ異なることを述べた. 従来研究として SCM 一種および NAND 型フラッシュメ モリー種を用いたハイブリッドストレージストレージの構成,および SCM を NAND 型フラ ッシュメモリの不揮発性キャッシュあるいは小容量ストレージとして用いるデータマネジメ ント手法について述べた. さらに不揮発性半導体メモリを用いた次世代のコンピュータアー キテクチャにおけるストレージの課題を論じた、ストレージアプリケーションの特性がさま ざまに異なるためストレージアプリケーション内のデータの特徴によって、異種の不揮発性 半導体メモリを用いたヘテロジニアスストレージの不揮発性半導体メモリの構成の最適化が 必要となる. またヘテロジニアスストレージの M-SCM あるいは S-SCM と NAND 型フラッ シュメモリとではアクセス頻度が異なり、不揮発性半導体メモリの種類によってエラー発生 頻度や許容書き換え回数が異なるため、それぞれに異なる強度の ECC を適用することが必要 となる. さらにストレージアプリケーションの特性によって最適な SCM 容量は異なり、デー タセンター事業者やユーザが手動でさまざまな種類のストレージアプリケーションに必要な SCM 容量を設定することは困難であるため、自動で SCM 容量を最適化する手法が必要であ ることを述べた.

## 参考文献

- [1] 柴山 潔, "コンピュータアーキテクチャの基礎"初版第9刷, 2010年, 近代科学社.

- [2] H. Ando, "コンピュータアーキテクチャ技術入門"初版第1刷, 2014年, 技術評論社.

- [3] R. F. Freitas and W. W. Wilcke, "Storage-class memory: The next storage system technology," *IBM* Journal of Research and Development, vol. 52, no. 4/5, pp. 439-447, Jul. 2008.

- [4] G. W. Burr, B. N. Kurdi, J. C. Scott, C. H. Lam, K. Gopalakrishnan, and R. S. Shenoy, "Overview of candidate device technologies for storage-class memory," IBM Journal of Research and Development, vol. 52, no. 4/5, pp. 449-464, Jul. 2008.

- [5] K. Tsuchida, T. Inaba, K. Fujita, Y. Ueda, T. Shimizu, Y. Asao, T. Kajiyama, M. Iwayama, K. Sugiura, S. Ikegawa, T. Kishi, T. Kai, M. Amano, N. Shimomura, H. Yoda, and Y. Watanabe, "A 64Mb MRAM with clamped reference and adequate-reference schemes," in IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, Feb. 2010, pp. 258-259.

- [6] S.-W. Chung, T. Kishi, J. W. Park, M. Yoshikawa, K. S. Park, T. Nagase, K. Sunouchi, H. Kanaya,

- G. C. Kim, K. Noma, M. S. Lee, A. Yamamoto, K. M. Rho, K. Tsuchida, S. J. Chung, J. Y. Li, H. S. Chun, H. Oyamatsu, and S. J. Hong, "4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure," in *IEEE International Electron Devices Meeting (IEDM) Technical Digest*, Dec. 2016, pp. 27.1.1-27.1.4.

- [7] A. Kawahara, R. Azuma, Y. Ikeda, K. Kawai, Y. Katoh, K. Tanabe, T. Nakamura, Y. Sumimoto, N. Yamada, N. Nakai, S. Sakamoto, Y. Hayakawa, K. Tsuji, S. Yoneda, A. Himeno, K. Origasa, K. Shimakawa, T. Takagi, T. Mikawa, and K. Aono, "An 8Mb multi-layered cross-point ReRAM macro with 43 MB/s write throughput," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 48, no. 1, pp. 178-185, Oct. 2013.

- [8] T.-Y. Liu, T. H. Yan, R. Scheuerlein, Y. Chen, J. K. Lee, G. Balakrishnan, G. Yee, H. Zhang, A. Yap, J. Ouyang, T. Sasaki, A. Al-Shamma, C. Chen, M. Gupta, G. Hilton, A. Kathuria, V. Lai, M. Matsumoto, A. Nigam, A. Pai, J. Pakhale, C. H. Siau, X. Wu, Y. Yin, N. Nagel, Y. Tanaka, M. Higashitani, T. Minvielle, C. Gorla, T. Tsukamoto, T. Yamaguchi, M. Okajima, T. Okamura, S. Takase, H. Inoue, and L. Fasoli, "A 130.7-mm2, 2-layer 32Gb ReRAM memory device in 24-nm technology," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 49, no. 1, pp. 140-153, Jan. 2014.

- [9] K. Kawai, A. Kawahara, R. Yasuhara, S. Muraoka, Z. Wei, R. Azuma, K. Tanabe, and K. Shimakawa, "Highly-reliable TaOx ReRAM technology using automatic forming circuit," in Proceedings of IEEE International Conference on IC Design and Technology (ICICDT), May 2014, pp. 100-103.

- [10] K.-J. Lee, B.-H. Cho, W.-Y. Cho, S. Kang, B.-G. Choi, H.-R. Oh, C.-S. Lee, H.-J. Kim, J.-M. Park, Q. Wang, M.-H. Park, Y.-H. Ro, J.-Y. Choi, K.-S. Kim, Y.-R. Kim, I.-C. Shin, K.-W. Lim, H.-K. Cho, C.-H. Choi, W.-R. Chung, D.-E. Kim, Y.-J. Yoon, K.-S. Yu, G.-T. Jeong, H.-S. Jeong, C.-K. Kwak, C.-H. Kim, K. Kim, "A 90nm 1.8 V 512 Mb diode-switch PRAM with 266 MB/s read throughput," *IEEE Journal of Solid-State Circuits (JSSC)*, vol. 43, no. 1, pp. 150-162, Jan. 2008.

- [11] Y. Choi, I. Song, M. Park, H. Chung, S. Chang, B. Cho, J. Kim, Y. Oh, D. Kwon, J. Sunwoo, J. Shin, Y. Rho, C. Lee, M. G. Kang, J. Lee, Y. Kwon, S. Kim, J. Kim, Y. Lee, Q. Wang, S. Cha, S. Ahn, H. Horii, J. Lee, K. Kim, H. Joo, K. Lee, Y. Lee, J. Yoo, and G. Jeong, "A 20nm 1.8V 8Gb PRAM with 40MB/s program bandwidth," in *IEEE International Solid-State Circuits Conference* (ISSCC) Diegest of Technical Papers, Feb. 2012, pp. 46-47.

- [12] Micron 3D XPoint Technology, https://www.micron.com/about/emerging-technologies/3d-xpoint-technology.

- [13] T. Hirofuchi and R. Takano, "RAMinate: Hypervisor-based virtualization for hybrid main memory

- systems," in Proceedings of ACM Symposium on Cloud Computing (SoCC), Oct. 2016, pp. 112-125.

- [14] F. Masuoka, M. Momodomi, Y. Iwata, and R. Shirota, "New ultra high density EPROM and flash EEPROM with NAND structure cell," in IEEE International Electron Devices Meeting (IEDM) Technical Digest, Dec. 1987, pp. 552-555.

- [15] R. H. Fowler and L. Nordheim, "Electron emission in intense electric fields," Proceedings of the Royal Society of London A: Mathematical, Physical and Engineering Sciences, vol. 119, no. 781, pp. 173-181, May 1928.

- [16] K. Takeuchi, "Novel co-design of NAND flash memory and NAND flash controller circuits for sub-30 nm low-power high-speed solid-state drives (SSD)," IEEE Journal of Solid-State Circuits (JSSC), vol. 44, no. 4, pp. 1227-1234, Apr. 2009.

- [17] P. Pavan, R. Bez, P. Olivo, and E. Zanoni, "Flash memory cells an overview," *Proceedings of the* IEEE, vol. 85, no. 8. pp. 1248-1271, Aug. 1997.

- [18] R. Bez, E. Camerlinghi, A. Modelli, and A. Visconti, "Introduction to flash memory," *Proceedings* of the IEEE, vol. 91, no. 4, pp. 489-502, Apr. 2003.

- [19] H. Niijima, "Design of a solid-state file using flash EEPROM," IBM Journal of Research and Development, vol. 39, no. 5, pp. 531-545, Sep. 1995.

- [20] K. Takeuchi, Y. Kameda, S. Fujimura, H. Otake, K. Hosono, H. Shiga, Y. Watanabe, T. Futatsuyama, Y. Shindo, M. Kojima, M. Iwai, M. Shirakawa, M. Ichige, K. Hatakeyama, S. Tanaka, T. Kamei, J.-Y. Fu, A. Cernea, Y. Li, M. Higashitani, G. Hemink, S. Sato, K. Oowada, S.-C. Lee, N. Hayashida, J. Wan, J. Lutze, S. Tsao, M. Mofidi, K, Sakurai, N. Tokiwa, H. Waki, Y. Nozawa, K. Kanazawa, and S. Ohshima, "A 56-nm CMOS 99-mm2 8-Gb multi-level NAND flash memory with 10-MB/s program throughput," IEEE Journal of Solid-State Circuits (JSSC), vol. 42, no. 1, pp. 219-232, Jan. 2007.

- [21] H. Fujii, K. Miyaji, K. Johguchi, K. Higuchi, C. Sun, and K. Takeuchi., "x11 performance increase, x6.9 endurance enhancement, 93% energy reduction of 3D TSV-integrated hybrid ReRAM/MLC NAND SSDs by data fragmentation suppression," in IEEE Symposium on VLSI Circuits Digest of Technical Papers, Jun. 2012, pp.134-135.

- [22] X.-Y. Hu, E. Eleftheriou, R. Haas, I. Iliadis, and R. Pletka, "Write amplification analysis in flashbased solid state drives," in Proceedings of ACM International Systems and Storage Conference (SYSTOR), May 2009, pp. 191-202.

- [23] Y. Koh, "NAND flash scaling beyond 20nm," in Proceedings of IEEE International Memory Workshop (IMW), May 2009, pp. 3-5.

- [24] M. Bauer, R. Alexis, G. Atwood, B. Baltar, A. Fazio, K. Frary, M. Hensel, M. Ishac, J. Javanifard, M. Landgraf, D. Leak, K. Loe, D. Mills, P. Ruby, R. Rozman, S. Sweha, S. Talreja, and K. Wojciechowski, "A multilevel-cell 32Mb flash memory," in *IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, Feb. 1995, pp. 132-133.

- [25] K. Takeuchi, T. Tanaka, and T. Tanzawa, "A multi-level cell architecture for high-speed programming multi-level NAND flash memories," in *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, Jun. 1997, pp. 67-68.

- [26] Y. Fukuzumi, R. Katsumata, M. Kito, M. Kido, M. Sato, H. Tanaka, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and A. Nitayama, "Optimal integration and characteristics of vertical array devices for ultra-high density, bit-cost scalable flash memory," in *IEEE International Electron Devices Meeting (IEDM) Technical Digest*, Dec. 2007, pp. 449-452.

- [27] S. Oshima and S. Fingerhut, "Flash memory is going places we have never been before," in *Flash Memory Summit*, Aug. 2017.

- [28] <u>C. Matsui</u>, Y. Yamaga, Y. Sugiyama, and K. Takeuchi, "8.9-times performance improvement by trihybrid storage system with SCM and MLC/TLC NAND flash memory," in *Extended Abstracts of International Conference on Solid State Devices and Materials (SSDM)*, Sep. 2016, pp. 105-106.

- [29] A. Faryushin, K. Seol, J. Na, S. Hur, J. Choi, and K. Kim, "The new program/erase cycling degradation mechanism of NAND flash memory devices," in *IEEE International Electron Devices Meeting (IEDM) Technical Digest*, Dec. 2009, pp. 823-826.

- [30] IBM Almaden Research Center, "Storage class memory: Towards a disruptively low-cost solid-state non-volatile memory," http://researcher.watson.ibm.com/researcher/files/us-gwburr/Almaden\_SCM\_overview\_Jan2013.pdf, Jan. 2013.

- [31] <u>C. Matsui</u>, T. Yamada, Y. Sugiyama, Y. Yamaga, and K. Takeuchi, "Optimal memory configuration analysis in tri-hybrid solid-state drives with storage class memory and multi-level cell/triple-level cell NAND flash memory," *Japanese Journal of Applied Physics (JJAP)*, vol. 56, no. 4S, pp. 04CE02-1 04CE02-9, Apr. 2017.

- [32] DRAMexchange, http://www.dramexchange.com.

- [33] X. Wu, J. Li, L. Zhang, E. Speight, and Y. Xie, "Power and performance of read-write aware hybrid cache with non-volatile memories," in *Proceedings of Design, Automation and Test in Europe Conference and Exhibition (DATE)*, Apr. 2009, pp. 737-742.

- [34] K. Abe, H. Noguchi, E. Kitagawa, N. Shimomura, J. Ito, and S. Fujita, "Novel hybrid DRAM/MRAM design for reducing power of high performance mobile CPU," in *IEEE*

- International Electron Devices Meeting (IEDM) Technical Digest, Dec. 2012, pp. 10.5.1-10.5.4.

- [35] G. Dhiman, R. Ayoub, and T. Rosing, "PDRAM: A hybrid PRAM and DRAM main memory system," in *Proceedings of Design Automation Conference (DAC)*, Jul. 2009, pp. 664-669.

- [36] Direct Access for files, https://www.kernel.org/doc/Documentation/filesystems/dax.txt.

- [37] G. Sun, Y. Joo, Y. Chen, D. Niu, Y. Xie, Y. Chen, and H. Li, "A hybrid solid-state storage architecture for the performance, energy consumption, and lifetime improvement," in *Proceedings* of International Symposium on High-Performance Computer Architecture (HPCA), Jan. 2010, pp. 141-152.

- [38] C. Sun, K. Miyaji, K. Johguchi, and K. Takeuchi, "A high performance and energy-efficient cold data eviction algorithm for 3D-TSV hybrid ReRAM/MLC NAND SSD," IEEE Transactions on Circuits and Systems-I (TCAS-I), vol. 61, no. 2, pp. 382-392, Feb. 2014.

- [39] S. Okamoto, C. Sun, S. Hachiya, T. Yamada, Y. Saito, T. O. Iwasaki, and K. Takeuchi, "Application driven SCM and NAND flash hybrid SSD design for data-centric computation system," in Proceedings of IEEE International Memory Workshop (IMW), May 2015, pp. 157-160.

- [40] T. Yamada, C. Matsui, and K. Takeuchi, "Optimal combinations of SCM characteristics and nonvolatile cache algorithm for high-performance SCM/NAND flash hybrid SSD," in Proceedings of *IEEE Silicon Nanoelectronics Workshop (SNW)*, Jun. 2016, pp. 88-89, poster presentation.

- [41] C. Matsui, C. Sun, and K. Takeuchi, "Design of hybrid SSDs with storage class memory and NAND flash memory," Proceedings of the IEEE, vol. 105, no. 9, pp. 1812-1821, Sep. 2017.

- [42] S. Hachiya, K. Johguchi, K. Miyaji, and K. Takeuchi, "TLC/MLC NAND flash mix-and-match design with exchangeable storage array," in Extended Abstracts of International Conference on Solid State Devices and Materials (SSDM), Sep. 2013, pp. 894-895.

- [43] S.-H. Shin, D.-K. Shim, J.-Y. Jeong, O.-S. Kwon, S.-Y. Yoon, M.-H. Choi, T.-Y. Kim, H.-W. Park, H.-J. Yoon, Y.-S. Song, Y.-H. Choi, S.-W. Shim, Y.-L. Ahn, K-T. Park, J.-M. Han, K.-H. Kyung, and Y.-H. Jun, "A new 3-bit programming algorithm using SLC-to-TLC migration for 8MB/s high performance TLC NAND flash memory," in IEEE Symposium on VLSI Circuits Digest of Technical Papers, Jun. 2012, pp. 132-133.

- [44] I. J. Chang and J.-S. Yang, "Bit-error rate improvement of TLC NAND flash using state re-ordering," IEICE Electronics Express (ELEX), vol. 9, no. 34, pp. 1775-1779, Dec. 2012.

- [45] MSR Cambridge Traces, http://iotta.snia.org/traces/388.

- [46] 新屋敷 裕太, 飯澤 健, 小沢 年弘, 荒堀 喜貴, 横田 治夫, "アクセス時間に基づいた字 アクセス予想によるデバイスミックスストレージシステムの制御手法",第8回データエ

学と情報マネジメントに関するフォーラム (DEIM Forum), 2016, pp. D8-2-1 - D8-2-6.

# 第3章 異種の不揮発性メモリを用いた ストレージ構成およびデータ管理アルゴリズム

## 3.1 はじめに

本章では複雑な特性を持つストレージアプリケーションを処理するため、異種の不揮発性 半導体メモリを用いたヘテロジニアスストレージを提案する。第2章で述べた従来研究と異 なり、三種以上の不揮発性半導体メモリを用いて構成したストレージをヘテロジニアススト レージと呼ぶ。ヘテロジニアスストレージの記憶として M-SCM、S-SCM、MLC NAND 型フ ラッシュメモリ、TLC NAND 型フラッシュメモリを用い、1)SCM、MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージ、および 2)M-SCM、S-SCM および NAND 型フラッシュメモリを用いたヘテロジニアスストレージを提案する。提案する二種類 のヘテロジニアスストレージは、不揮発性半導体メモリ特性の長所を用いる一方で、それぞ れの不揮発性半導体メモリの短所を隠ぺいする。

### 3.2 不揮発性メモリの読み出し、書き込み時間

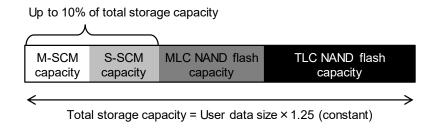

本研究において M-SCM および S-SCM を用いる理由はそれらのアクセス性能の高さであり、TLC NAND 型フラッシュメモリを用いる理由はその低いビットコストである。第2章で述べたように、TLC NAND 型フラッシュメモリは MLC NAND 型フラッシュメモリと比較して読み出し・書き込み時間が長いが、そのビットコストは約2/3である。従来の SCM と MLC NAND 型フラッシュメモリを用いたハイブリッドストレージでは、SCM によるストレージコストの増加が問題であった。表2.1 および表2.2 で定めたように、M-SCM、S-SCM(scenario 2)、MLC NAND 型フラッシュメモリ、TLC NAND 型フラッシュメモリのビットコスト比は、10:6:1:2/3 である。M-SCM、S-SCM、MLC および TLC NAND 型フラッシュメモリを用いる場合の総ストレージコストの計算式を式(3.1)に示す。

Total storage cost

$$= \sum_{M-SCM.S-SCM.MLC \text{ flash.TLC flash}} (memory \text{ capacity ratio} \times \text{bit cost ratio})$$

(3.1)

本論文において、総ストレージコストはヘテロジニアスストレージの不揮発性半導体メモリの容量とそれらのビットコストで求められるとする.式(3.1)から SCM によるストレージコストの増加は、低いビットコストの TLC NAND 型フラッシュメモリを用いることで相殺できることがわかる.

SCM は NAND 型フラッシュメモリと同様に不揮発性半導体メモリであるが、第2章で述 べたようにこれらの特性はさまざまな点で異なる. SCM はセクタ (あるいはブロック, 512 Byte) 単位で読み出し・書き込み動作が可能であるため、SCM に保存された古いデータを上 書きすることが可能である.一方で MLC NAND 型フラッシュメモリはページ (32 セクタ, 16 KByte) 単位で読み出し・書き込みを行い, ブロック (256 page, 4.0 MByte) 単位で消去す る. MLC NAND 型フラッシュメモリは 128 ワードラインを持ち, 1 ワードライン当たり Upper page, Lower page を持つので、1 ブロック当たりのページ数は 256 であると仮定する. また TLC NAND 型フラッシュメモリはページ (16 KByte) 単位で読み出し, ブロック (258 page, 4.03 MByte) 単位で書き込み・消去を行う. TLC NAND 型フラッシュメモリは 86 ワードライ ンを持ち、1 ワードライン当たり Upper page、Middle page、Lower page を持つため、1 ブロッ ク当たりのページ数は 258 であると仮定する. このため MLC NAND 型フラッシュメモリの 1ページ内のデータを上書きするとき、上書きするデータを有するページを読み出し、上書き するデータとともにコントローラで統合して新しいページに書き込む必要がある.さらに第 2.4.2 節で述べたように TLC NAND 型フラッシュメモリはセル間干渉を防ぐためブロック書 き込みをする必要がある. TLC NAND 型フラッシュメモリの 1 ページ内のデータを上書きす るとき、上書きするデータを有するページおよびそのページが存在するブロックの他の有効 ページも読み出し、別の新しいブロックに書き込み必要がある. 悪い条件として 1 セクタの みを上書きすることを考えると、表 2.1 より M-SCM の場合は 0.1 μsec, S-SCM (scenario 2) の場合は 1 μsec だけ時間を要する.一方で MLC および TLC NAND 型フラッシュメモリの読 み出し・書き込み時間として表 2.2 に示す Upper/Middle/Lower page から求めた平均読み出し・ 書き込み時間を用いると、MLCNAND型フラッシュメモリの1セクタを上書きするのに要す る時間は

1 sector overwrite time of MLC NAND flash

= 1 page  $\times$  (average page read time + average page write time)

(3.2)

= 1 page  $\times$  (44  $\mu sec + 1185 \mu sec$ )

= 1.3 msec

となり、TLC NAND型フラッシュメモリの1セクタを上書きするのに要する時間は

1 sector overwrite time of TLC NAND flash

= # of page in block

$$\times$$

(average page read time + average page write time) (3.3)

= 258 page  $\times$  (87  $\mu sec + 2180 \mu sec$ )

=585 msec

と計算することができる. さらに悪いことに、NAND 型フラッシュメモリは無効ページを消去し空ページを確保するガベージコレクション (garbage collection, GC) 動作を要する. 例としてブロック内の有効ページ数が 100 のとき、MLC および TLC NAND 型フラッシュメモリの GC に必要な時間は次の式 (3.4) および式 (3.5) のように計算できる.

GC time of MLC NAND flash

= # of valid pages

$$\times$$

(average page read time + average page write time)

+ block erase time (3.4)

- = 100 page  $\times$  (44  $\mu sec + 1185 \mu sec$ ) + 3300  $\mu sec$

- = 126 msec

GC time of TLC NAND flash

= # of valid pages  $\times$  (average page read time + average page write time) + block erase time (3.5)

- = 100 page  $\times$  (87  $\mu sec + 2180 \mu sec$ ) + 3200  $\mu sec$

- = 230 msec

実際の TLC NAND 型フラッシュメモリにおいては、SRAM キャッシュや TLC NAND 型フラッシュメモリを SLC モードで使うなどして、ブロック書き込みに要する時間を削減する努力をしている[1]. 一方で1セクタを読み出すとき、表 2.1 より M-SCM は 0.1 µsec, S-SCM (scenario 2) は 1.0 µsec を要する.また NAND 型フラッシュメモリ内の 1 セクタを読み出すときそのセクタを含む 1 ページ全体を読み出すことが必要となり、MLC および TLC NAND 型フラッシュメモリでそれぞれ平均して 44 µsec、87 µsec を要する.SCM と NAND 型フラッシュメモリの書き込み時間の差と比較して、読み出し時間の差は十分小さいことがわかる.ただし本論文では、TLC NAND 型フラッシュメモリの書き込み単位はページであると仮定し第 4 章の評価を行なった.

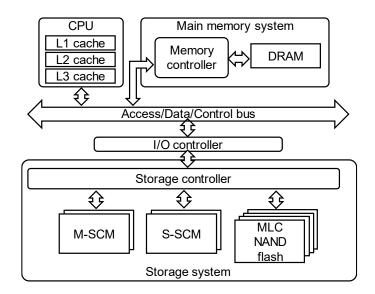

図 3.1 SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージ [2]

## 3.3 SCM, MLC および TLC NAND 型フラッシュメモリを用いたストレージ

図 3.1 に SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアススト レージのアーキテクチャを示す[2]. SCM は用途に応じて M-SCM あるいは S-SCM のいずれ かを用い、さらに MLC および TLC NAND 型フラッシュメモリを用いる. 第 3.2 節で議論し たようにSCMとMLCおよびTLCNAND型フラッシュメモリは書き込み特性が特に異なる. また SCM (M-SCM あるいは S-SCM) はそのビットコストの高さから,データセンターでの 実用上, MLC および TLC NAND 型フラッシュメモリと比較すると小容量しか用いることが できないと考えられる.そのため本研究で提案する SCM,MLC および TLC NAND 型フラッ シュメモリを用いたヘテロジニアスストレージでは書き込み動作に適したデータマネジメン トアルゴリズムを用いる. 第 2.4.1 項で述べたコールドデータエビクション (Cold Data Eviction, CDE) [3]およびラウンドロビン・フローズンデータコレクションアルゴリズム (Round-Robin Frozen Data Collection Algorithm, RR-FDCA) [4]はそれぞれ, 不揮発性半導体メモリの特性を 考慮した書き込み動作に適したデータマネジメントアルゴリズムである.CDE は SCM およ び MLC NAND 型フラッシュメモリを用いたハイブリッドストレージにおいて, 書き込みデ ータの特性から SCM あるいは MLC NAND 型フラッシュメモリに書き込むことを判断する. また RR-FDCA は MLC および TLC NAND 型フラッシュメモリを用いたハイブリッドストレ ージにおいて、MLC NAND 型フラッシュメモリの上書きされないデータを TLC NAND 型フ

図 3.2 SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージ に適用するコールドアンドフローズンデータエビクション (Cold and Frozen Data Eviction, CFDE) アルゴリズム [2]

ラッシュメモリに書き移す. この 2 つのデータマネジメントアルゴリズムを組み合わせることで、SCM には頻繁にアクセスされるホットデータ(hot data)、MLC NAND 型フラッシュメモリにはアクセス頻度の低いコールドデータ(cold data)、さらに TLC NAND 型フラッシュメモリにはほとんどアクセスの無いフローズンデータ(frozen data)をそれぞれ保存する. SCM はストレージシステムの性能を向上させ、TLC NAND 型フラッシュメモリは SCM によるコスト上昇を均衡させストレージ容量を増やす. 図 1.1 のメモリおよびストレージ階層と同様に、MLC NAND 型フラッシュメモリは SCM と TLC NAND 型フラッシュメモリとの間の中間的なストレージとして機能する.

以下に SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジアスストレージに適用するデータマネジメントアルゴリズムの詳細を述べる. このアルゴリズムをコールドアンドフローズンデータエビクション (Cold and Frozen Data Eviction, CFDE) と呼び,動作を図 3.2 に示す. 提案の SCM, MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージでは、SCM と MLC NAND 型フラッシュメモリ間は CDE アルゴリズム, MLC および TLC NAND 型フラッシュメモリ間は RR-FDCA を用いる. まずホストから書き込みリクエストを受け取ると、CDE アルゴリズムに従ってデータを書き込む. CDE アルゴリズムでは固定長の least recently used (LRU) テーブルを用いて SCM 内のデータの書き込み順を管理する. 本研究では LRU リストのサイズは従来研究の結果[3]より SCM 容量の 80%とした. LRU リストは SCM に保存された論理ページアドレス (logical page address, LPA) の

順番を記録する. LPA は式 (3.6) のように、論理ブロックアドレス (logical block address, LBA) から求められる.

$$LPA = \frac{LBA}{NAND \text{ flash page size } (= 16 \text{ } KByte)}$$

(3.6)

CDE アルゴリズムでは LRU リストに LPA のアクセス順序を記録するほか、頻繁にアクセス されるホットデータを判断するの役割も持つ.

図 2.14 (b) に示したように、ホストからの新しい書き込みデータは初めにデータの大きさ を判断する.書き込みリクエストのデータサイズが NAND 型フラッシュメモリのページサイ ズの半分である 8 KByte と比較して小さい場合ランダム (random) と判断する. 反対に書き 込みリクエストのデータサイズが 8 KByte より大きい場合をシーケンシャル (sequential) と する.シーケンシャルと判断されたデータで LRU リストにあるデータはホットと判断され る. したがって、ホットあるいはランダムなデータは SCM へ (図 3.2 Hot or random write operation), コールドかつシーケンシャルなデータは MLC NAND 型フラッシュメモリへ (図 3.2 Cold and sequential write operation) 書き込む. SCM ヘデータを書き込むべきデータを判断 した後, SCM 内の容量がすでにデータでいっぱいか否かを判断する. 本研究では従来研究[3] と同様に、SCM 容量のうち空の容量が 20%以上あれば新しいデータを書き込むのに十分であ るとした. SCM 内の空の容量が 20%以上あるとき, ホストからのホットあるいはランダムな データは SCM へすぐに書き込む. しかし SCM 内の空の容量が 20%未満の場合, 新しいデー タを書き込むのに不十分であるとして、SCM から MLC NAND 型フラッシュメモリへ頻繁に アクセスされないコールドデータを evict する必要がある. まず LRU リストを用いて SCM 内 のデータがコールドであるか判断する. LRU リストに存在しないコールドデータは続いて, 物理ページ内で断片化(fragmentation)しているかを判断する. MLC NAND 型フラッシュメ モリの物理ページサイズ (16 KByte) の 60%より少ないデータがある場合, そのページは断 片化しているという[3]. 参考文献[3]と同様に SCM 容量およびストレージアプリケーション 特性に依らず, SCM 内で 4,000 ページ分のコールドかつシーケンシャルデータが集まると, それらのデータを SCM から MLC NAND 型フラッシュメモリヘ evict する (図 3.2 Cold data eviction operation). また, MLC NAND 型フラッシュメモリに保存されたデータを上書きする 場合がある.この場合もまたLRUリストを用いて上書きする古いデータがホットでさらに断 片化していれば、NAND 型フラッシュメモリの同一ページに存在する有効なデータと一緒に SCM へ書き込む. 一方でホストからの読み出しリクエストを受け取った時, データが保存さ れた SCM あるいは MLC NAND 型フラッシュメモリから読み出す. つまり頻繁に読み出しリ

クエストがあるデータでも MLC NAND 型フラッシュメモリから読み出し、SCM へのデータ コピーやデータの移動は行わない. そのため、CDE アルゴリズムは書き込みリクエストに適 したアルゴリズムであると言える.

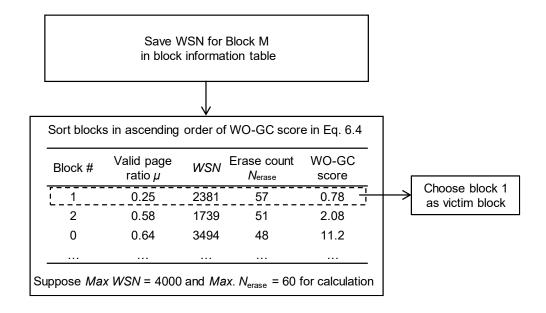

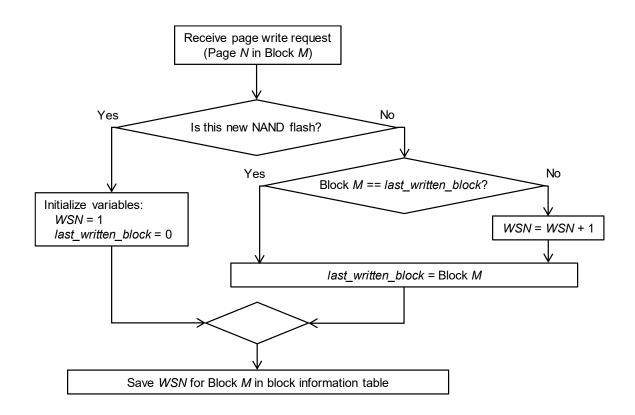

次に MLC NAND 型フラッシュメモリから TLC NAND 型フラッシュメモリへの eviction に ついて述べる (図 3.2 Frozen data eviction operation). MLC NAND 型フラッシュメモリに多く のデータが書き込まれガベージコレクションが必要になると、RR-FDCA [4]に従って MLC NAND 型フラッシュメモリから TLC NAND 型フラッシュメモリヘデータを evict する. MLC NAND 型フラッシュメモリの GC 動作で消去するブロックは, MLC NAND 型フラッシュメモ リで初めに書き込まれた最も古いブロックをラウンドロビン方式で選択する. ラウンドロビ ン方式の GC は言い換えると、NAND 型フラッシュメモリで最も消去回数の少ないブロック を選択することである. NAND 型フラッシュメモリのブロックのウエアレベリングを達成す るためにラウンドロビン方式の GC (round-robin GC, RR-GC) を適用した. しかし RR-GC に NAND 型フラッシュメモリの性能を劣化させる問題があることを第 6.3 節で議論する. RR-FDCA では MLC NAND 型フラッシュメモリの GC 対象となるブロックを選択した後, そのブ ロックが上書きの少ないフローズンであるかを判断する. 第2.3 節で述べたように, NAND型 フラッシュメモリのページに上書きを行うと、古いデータを含むページを読み出し上書きし たいデータと統合して別のページに書き込む、そして上書きされたページは無効ページとし て管理される. つまり RR-GC を用いる場合 GC 動作が NAND 型フラッシュメモリ内のブロ ックを一周する間に、上書きされたページは無効ページとなり、上書きされなかったページ は有効ページのまま存在する. このように NAND 型フラッシュメモリではページの有効・無 効によって、上書きされたか否かが判断できる. MLC NAND 型フラッシュメモリ内の有効ペ ージ数がブロックサイズの 75%以上[5]ある場合, そのブロックはホットであるとして MLC NAND 型フラッシュメモリ内で GC を行う. つぎに図 2.15 (b) に示した RR-GC のコールド データスクリーニングが 2回以上行われた MLC NAND 型フラッシュメモリのブロックを選 択することで、ほとんど上書きされないフローズンなデータを含む MLC NAND 型フラッシ ュメモリのブロックをGC対象とする. 続いてGC対象となったフローズンデータを含むMLC NAND 型フラッシュメモリのブロックの有効ページを TLC NAND 型フラッシュメモリへ書 き込む. 最後に有効ページを TLC NAND 型フラッシュメモリへ移動した後の MLC NAND 型 フラッシュメモリのブロックを消去する. なお, NAND 型フラッシュメモリのページ読み出 しを行っても、ページの有効・無効は変化しない. さらに、ホストからの読み出しリクエス トを受け取った時、データが保存された MLC あるいは TLC NAND 型フラッシュメモリから

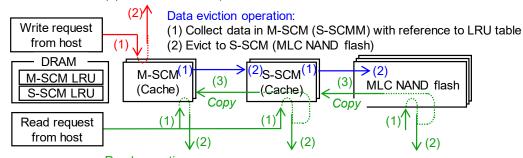

図 3.3 M-SCM, S-SCM および MLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージ [6]

読み出す. つまり頻繁に読み出しリクエストがあるデータでも TLC NAND 型フラッシュメモリから読み出し, MLC NAND 型フラッシュメモリへのデータコピーやデータの移動は行わない. そのため, RR-FDCA もまた書き込みリクエストに適したアルゴリズムであると言える.

## 3.4 M-SCM, S-SCM および NAND 型フラッシュメモリを用いたストレージ

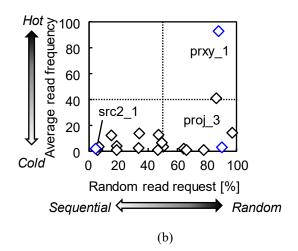

図 3.3 に M-SCM、S-SCM および MLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージのアーキテクチャを示す[6]. 第 3.2 節で議論したように、M-SCM のビットコストは MLC NAND 型フラッシュメモリと比較して約 10 倍であるため、データセンターでの実用上小容量しか用いることができないと考えられる。また表 2.2 に示したように、M-SCM と S-SCM(scenario 2)の読み出し・書き込み時間は約 10 倍の差である。しかし、S-SCM と MLC NAND 型フラッシュメモリの読み出し時間の差は平均で 44 倍、書き込み時間の差は下均で約 1200 倍と大きな差がある。さらにデータ上書きを行う場合は書き込み時間の差は広がる。そのため M-SCM、S-SCM および MLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージでは、M-SCM および S-SCM へのアクセスが多く MLC NAND 型フラッシュメモリへのアクセスが少ないアルゴリズムが必要である。第 2.4 節で議論した不揮発性半導体メモリ向けライトバック(NV-WB)キャッシュを発展させた、二種類の SCM を用いたライトバック(2 Non-Volatile Memory Write-Back、2NV-WB)キャッシュデータマネジメントアルゴリズムを提案する。書き込みの多いアプリケーションに対して性能向上する CDE を基にした

#### Write operation:

- (1) Write to M-SCM and update LRU table

- (2) Return "write complete" to host

Read operation:

- (1) Read from M-SCM, S-SCM or MLC NAND flash

- (2) Return "read complete" to host

- (3) Copy data to M-SCM (S-SCM) if read from S-SCM (MLC NAND flash)

図 3.4 二種類の SCM および MLC NAND 型フラッシュメモリを用いたライトバック (2 Non-Volatile Memory Write-Back, 2NV-WB) キャッシュデータマネジメントアルゴリズム [6]

アルゴリズムと異なり、書き込みおよび読み出しの多いアプリケーションに対して性能向上を行うことができると考える. SCM を二種類用いて極端にアクセス頻度の高いデータを M-SCM に、ややアクセス頻度の高いデータを S-SCM に保存することを目的とする.

図3.4に二種類のSCMおよびMLC NAND型フラッシュメモリを用いたライトバック(2NV-WB) キャッシュデータマネジメントアルゴリズム[6]を示す. 一種類のSCMを用いるNV-WB [7]と同様に、M-SCM および S-SCM の不揮発性のため2NV-WB キャッシュは定期的なデータフラッシュ動作が不要で、突然の電源障害に対して安全である. 初めに2NV-WB キャッシュアルゴリズムの書き込み動作について述べる. すべてのデータは初めに、S-SCM の不揮発性キャッシュメモリとしてのM-SCM に書き込まれる(図3.4 Write operation). M-SCM 内に書き込まれた順番を管理するために、M-SCM LRU リストを用いる. CDE アルゴリズムで SCM 内のデータアクセス順序を管理しデータのホットあるいはコールドを判断する LRU リストと異なる点は、2NV-WB キャッシュアルゴリズムで用いる M-SCM LRU リストは LPA のほかに 1 bit の clean/dirty flag を必要とすること、また M-SCM 容量全体を表現するリストサイズが必要なことである. 2NV-WB キャッシュアルゴリズムでは、M-SCM と S-SCM 間で同じデータを保存し一貫性が保たれている場合をクリーンデータ(clean data)と呼び clean flag "0"を、M-SCM にしかデータが無い場合はダーティデータ(dirty data)と呼び dirty flag "1"をたてる。M-SCM の空き容量が残り 20%未満になると evict 動作を発動する。M-SCM の空き容量が20%以上になるまで、LRU 順にアクセス頻度の少ないデータを M-SCM から S-SCM へ evict

する(図 3.4 Evict operation). S-SCM は M-SCM から evict されたデータおよび後述する MLC NAND 型フラッシュメモリから書き戻されたデータを保存する. S-SCM は MLC NAND 型フラッシュメモリの不揮発性キャッシュとして動作する. M-SCM LRU と同様に、S-SCM 内のデータのアクセス順序および clean/dirty flag を管理するために S-SCM LRU リストを用いる. S-SCM と MLC NAND 型フラッシュメモリとの間でデータの一貫性があればクリーンデータ (clean data) であるため clean flag "0"を、M-SCM にしかデータが無い場合はダーティデータ (dirty data) であり dirty flag "1"をたてる。さらに S-SCM の空き容量が減少すると、S-SCM から MLC NAND 型フラッシュメモリヘデータを evict する. S-SCM の空き容量が 20%以上になるまで、S-SCM LRU リストに従いアクセス頻度の低いデータを S-SCM から MLC NAND 型フラッシュメモリは大容量の不揮発性半導体メモリとして機能し、S-SCM から evict されたデータを保存する. M-SCM および S-SCM と異なり、MLC NAND 型フラッシュメモリのデータアクセス順序を管理するための LRU リストは用いない.

M-SCM LRU リストに基づいた M-SCM から S-SCM への eviction および S-SCM LRU リストに基づいた S-SCM から MLC NAND 型フラッシュメモリへの eviction は、evict すべきデータがクリーンあるいはダーティによって動作が異なる。第 2.4 節で述べた SCM および NAND型フラッシュメモリを用いたストレージ向けの NV-WB キャッシュアルゴリズムと同様に、クリーンデータの場合は上位の不揮発性半導体メモリ(M-SCM あるいは S-SCM)から下位の不揮発性半導体メモリ(M-SCM あるいは S-SCM)から下位の不揮発性半導体メモリ(M-SCM あるいは S-SCM)から下位の不揮発性半導体メモリ(S-SCM あるいは MLC NAND型フラッシュメモリ)へデータを移動する必要は無い。一方、ダーティデータの場合は上位の不揮発性半導体メモリ(M-SCM あるいは S-SCM)から下位の不揮発性半導体メモリ(S-SCM あるいは MLC NAND型フラッシュメモリ)へデータを移動する必要がある。第 2.3 節および第 3.2 節で議論したように、M-SCM と S-SCM のアクセス性能差と比較して、S-SCM と MLC NAND型フラッシュメモリのアクセス性能の差は大きく、さらに MLC NAND型フラッシュメモリは GC が必要である。そのため、S-SCM から MLC NAND型フラッシュメモリへ多くのデータが evict されると、ストレージ性能全体を低下させる。このことから S-SCM と MLC NAND型フラッシュメモリとの間では、できるだけデータの一貫性(クリーン)を保つ方がよいと考える。

続いて上書き動作について述べる. M-SCM に保存されたデータを上書きするとき、その場での上書きが可能である. 上書きされるデータ LPA はもっとも最近にアクセスがあったとして、M-SCM LRU リストの先頭に移動する. S-SCM もその場での上書きが可能であるが、今後頻繁に上書きや読み出しがある可能性を考慮してより高速な M-SCM に書き込む. その後、

M-SCM LRU リストの先頭に移動し、一方で S-SCM の上書きされたデータは消去する.また、MLC NAND 型フラッシュメモリに上書きするときの動作は第 2.4 節で述べた SCM および NAND 型フラッシュメモリを用いたハイブリッドストレージに用いる NV-WB キャッシュアルゴリズムと同じである. MLC NAND 型フラッシュメモリの上書きされるデータを含むページを読み出し、上書きしたいデータと統合して S-SCM に書き込む. このとき上書きしたデータを含む LPA は、S-SCM LRU リストの先頭である MRU の位置に移動する.

続いて 2NV-WB の読み出し動作について述べる(図 3.4 Read operation). M-SCM に保存されたデータを読み出すときは、M-SCM から読み出し、M-SCM LRU リストの先頭に移動する. S-SCM に保存されたデータを読み出すときは、初めに S-SCM から読み出しストレージコントローラへデータを伝える.次に S-SCM から読み出したデータを M-SCM へコピーする. M-SCM LRU リストの先頭に、 S-SCM LRU リストの先頭に、 読み出したデータの順序を移動する. また、MLC NAND 型フラッシュメモリから読み出すとき、第 2.4 節で述べた NV-WB キャッシュアルゴリズムと同様、MLC NAND 型フラッシュメモリからデータを読み出しストレージコントローラへ返す. 次に MLC NAND 型フラッシュメモリから読み出したデータを S-SCM へコピーする. その後、 S-SCM LRU リストの先頭へ読み出したデータの順序を移動する. M-SCM と MLC NAND 型フラッシュメモリは性能差および容量差が大きいため、MLC NAND 型フラッシュメモリから M-SCM へ直接データをコピーしない管理方式を設計した. 読み出し動作は上書き動作と似ているが、下位のメモリから上位のメモリへデータをコピーするときに、下位メモリのデータをそのまま保存する点が異なる. 下位メモリから上位メモリヘデータを移動ではなくコピーするため、上位のメモリおよび下位のメモリで同じデータを持つ場合がある.これがクリーンデータとなる.

このように 2NV-WB では M-SCM と S-SCM 間, および S-SCM と MLC NAND 型フラッシュメモリ間でデータの移動が発生する. しかし M-SCM と MLC NAND 型フラッシュメモリ間のアクセス性能差を考慮し, M-SCM と MLC NAND 型フラッシュメモリ間ではデータの移動はしないとした. しかし, M-SCM および S-SCM の容量は MLC NAND 型フラッシュメモリと比較して小さいと考えられるため,参考文献[8]で明らかにしたように読み出しの多いアプリケーションに対して, M-SCM と S-SCM との間で循環するデータがストレージ性能を低下させる可能性がある. そのために, L2 キャッシュ向けのデータ管理方法[9]を参考に, M-SCM および S-SCM 間のデータ移動を減らす仕組みを取り入れた. 2NV-WB キャッシュアルゴリズムにおいては, S-SCM LRU に保存されたデータはそれぞれ (Read\_count, Write\_count)をペアで持つ. まず, M-SCM から evict されたデータは、(Read\_count, Write\_count) = (0,0)

で S-SCM LRU に登録される. MLC NAND 型フラッシュメモリへの上書きや読み出しによって S-SCM LRU へ登録されたデータもまた (Read\_count, Write\_count) = (0,0) で S-SCM LRU に登録される. S-SCM に保存されたデータに読み出しリクエストがあった場合 Read\_count を インクリメントする. 同様に S-SCM に保存されたデータに上書きリクエストがあった場合 Write\_count をインクリメントする. (Read\_count, Write\_count) を導入しない場合, S-SCM に保存されたデータに一度でも読み出しあるいは上書きリクエストがあれば, そのデータは M-SCM にコピーあるいは書き込まれる. S-SCM LRU に (Read\_count, Write\_count) を導入することによって, Read\_count が Read\_threshold あるいは Write\_count が Write\_threshold を超えた場合だけ, S-SCM から M-SCM へのデータ移動が発生する. S-SCM からの読み出し動作では M-SCM にデータをコピーした後, M-SCM でそのデータに上書きが無ければ M-SCM と S-SCM との間でクリーンとして保たれる. その後 M-SCM から S-SCM への evict するときのオーバーヘッドが少ないため, 本論文では Read\_threshold=5, Write\_threshold=10 として第4章で性能評価を行なう.

## 3.5 まとめ

本章では異種の不揮発性半導体メモリを用いたヘテロジニアスストレージ構成およびそのデータマネジメントアルゴリズムを述べた. 従来研究と異なり、三種以上の不揮発性半導体メモリを用いて構成したストレージをヘテロジニアスストレージと呼び本論文で扱う. ヘテロジニアスストレージとして、1)SCM、MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージおよび 2)M-SCM、S-SCM および NAND 型フラッシュメモリを用いたヘテロジニアスストレージを提案した. 第一の SCM、MLC および TLC NAND 型フラッシュメモリを用いたヘテロジニアスストレージと比較して、MLC および MLC NAND 型フラッシュメモリに滞留するアクセス頻度の低いデータを TLC NAND 型フラッシュメモリに保存することで MLC NAND 型フラッシュメモリの書き換え回数を削減することを目的とする. さらに SCM の導入で上昇する総ストレージコストをビットコストの低い TLC NAND 型フラッシュメモリで均衡することができる. 第二の M-SCM、S-SCM および NAND 型フラッシュメモリを用いたヘテロジニアスストレージは、SCM を二種類用いて極端にアクセス頻度の高いデータを M-SCM に、ややアクセス頻度の高いデータを S-SCM に保存することを特徴とする.

# 参考文献

- [1] S.-H. Shin, D.-K. Shim, J.-Y. Jeong, O.-S. Kwon, S.-Y. Yoon, M.-H. Choi, T.-Y. Kim, H.-W. Park, H.-J. Yoon, Y.-S. Song, Y.-H. Choi, S.-W. Shim, Y.-L. Ahn, K-T. Park, J.-M. Han, K.-H. Kyung, and Y.-H. Jun, "A new 3-bit programming algorithm using SLC-to-TLC migration for 8MB/s high performance TLC NAND flash memory," in *IEEE Symposium on VLSI Circuits Digest of Technical Papers*, Jun. 2012, pp. 132-133.

- [2] <u>C. Matsui</u>, Y. Yamaga, Y. Sugiyama, and K. Takeuchi, "8.9-times performance improvement by trihybrid storage system with SCM and MLC/TLC NAND flash memory," in *Extended Abstracts of International Conference on Solid State Devices and Materials (SSDM)*, Sep. 2016, pp. 105-106.

- [3] C. Sun, K. Miyaji, K. Johguchi, and K. Takeuchi, "A high performance and energy-efficient cold data eviction algorithm for 3D-TSV hybrid ReRAM/MLC NAND SSD," *IEEE Transactions on Circuits and Systems-I (TCAS-I)*, vol. 61, no. 2, pp. 382-392, Feb. 2014.

- [4] S. Hachiya, K. Johguchi, K. Miyaji, and K. Takeuchi, "TLC/MLC NAND flash mix-and-match design with exchangeable storage array," in *Extended Abstracts of International Conference on Solid State Devices and Materials (SSDM)*, Sep. 2013, pp. 894-895.

- [5] S. Hachiya, K. Johguchi, K. Miyaji, and K. Takeuchi, "Hybrid triple-level-cell/multi-level-cell NAND flash storage array with chip exchangeable method," *Japanese Journal of Applied Physics* (*JJAP*), vol. 53, no. 4S, pp. 04EE04-1 04EE04-10, Apr. 2014.

- [6] <u>C. Matsui</u> and K. Takeuchi, "22% higher performance, 2x SCM write endurance heterogeneous storage with dual SCM and NAND flash memory," in *Proceedings of European Solid-State Device Research Conference (ESSDERC)*, Sep. 2017, pp. 6-9.

- [7] S. Okamoto, C. Sun, S. Hachiya, T. Yamada, Y. Saito, T. O. Iwasaki, and K. Takeuchi, "Application driven SCM and NAND flash hybrid SSD design for data-centric computation system," in *Proceedings of IEEE International Memory Workshop (IMW)*, May 2015, pp. 157-160.

- [8] T. Yamada, <u>C. Matsui</u>, and K. Takeuchi, "Workload-based co-design of non-volatile cache algorithm and storage class memory specifications for storage class memory/NAND flash hybrid SSDs," *IEICE Transactions on Electronics*, vol. E100-C, no. 4, pp. 373-381, Apr. 2017.

- [9] X. Wu, L. Li, L. Zhang, E. Speight, and Y. Xie, "Power and performance of read-write aware hybrid cache with non-volatile memories," in *Proceedings of Design, Automation and Test in Europe Conference and Exhibition (DATE)*, Apr. 2009, pp. 737-742.

# 第4章 アプリケーションに応じた 不揮発性メモリの選択

## 4.1 はじめに

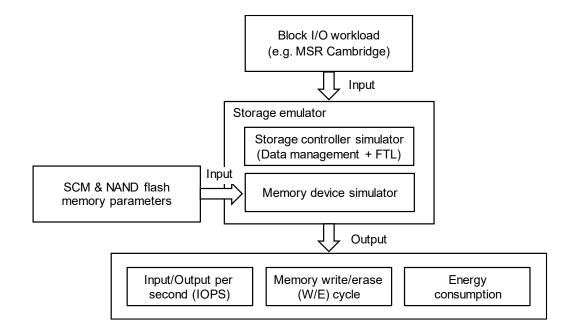

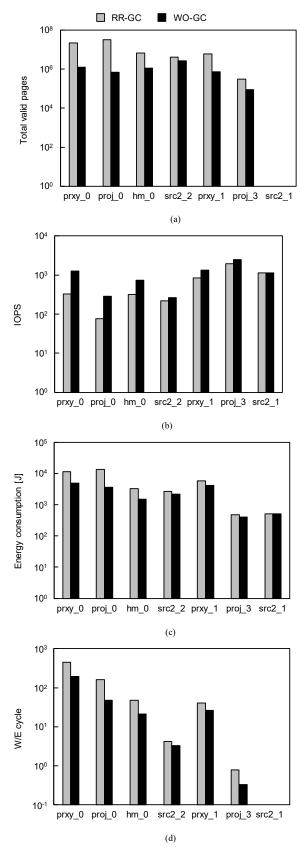

本章では、第3章で提案した二種類の異種メモリを用いたヘテロジニアスストレージの性能評価を行なう。SystemC ベースのストレージエミュレータに、不揮発性半導体メモリの動作およびデータマネジメントアルゴリズムを実装する。不揮発性半導体メモリの容量比や書き込み・読み出し時間などのアクセス性能を変化させ、ヘテロジニアスストレージのアクセス性能、消費エネルギー、不揮発性半導体メモリの書き換え回数の点から評価し比較する。代表的なストレージアプリケーション毎にヘテロジニアスストレージの最適な不揮発性半導体メモリ構成を示す。

## 4.2 評価環境

ペテロジニアスストレージの性能を評価し、アプリケーション特性に最適なメモリ構成を提示するため、SystemCを用いた transaction-level modeling(TLM)ベースのエミュレータを用いる[1]. TLM ではデータの書き込みや読み出しという転送単位ごとに抽象度の高いモデリングを行う。Register transfer level(RTL)ベースのエミュレータと比較すると、TLM は高速なシミュレーションが可能である。図 4.1 に示すように、ストレージエミュレータは、論理・物理アドレス変換、ウエアレベリング、GC などの flash translation layer(FTL)の機能および不揮発性半導体メモリ間のデータマネジメントアルゴリズムをモデル化している。NAND型フラッシュメモリの論理アドレス・物理アドレス変換は、ページレベルマッピング[2][3][4]を用いる。ストレージの合計容量は各アプリケーションによって異なり、アプリケーションの最大アクセスアドレスにNAND型フラッシュメモリのオーバープロビジョニング容量として25%上乗せした。オーバープロビジョニング容量はNAND型フラッシュメモリに追加される容量であり、オーバープロビジョニング容量が多いとガベージコレクションの頻度が減少し性能が向上する。ストレージエミュレータの入力はログベースのトレースであり、本論文では図 2.16 で特性ごとに分類した MSR Cambridge のトレース[5]を用いる。特性分類した各カ

図 4.1 SystemC を用いた TLM ベースのエミュレータ概要 [1][6]

テゴリから1アプリケーションずつ選択し, prxy\_0, proj\_0, hm\_0, src2\_2, prxy\_1, proj\_3, src2 1 の 7 種を用いる. また、書き込み・読み出し時間、メモリコア数、I/O 電力のようなメ モリに関するパラメータは表 2.1 および表 2.2 に示した不揮発性半導体メモリの特性を入力 として用いる. 本章では、異なる特性を持つ不揮発性半導体メモリは各 1 チップとし、同じ 種類の不揮発性半導体メモリ間で並列動作を行わないこととした. さらにデータマネジメン トアルゴリズムを実装し、用いる不揮発性半導体メモリによってデータ管理手法を変更する ことができる. シミュレーションが終わると, ストレージ性能 (Input/Output per second, IOPS), メモリの書き換え回数、消費エネルギーを出力する[6].

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consuming time of (read operation + write operation)}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consumption}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consumption}}$$

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consumption}}$$

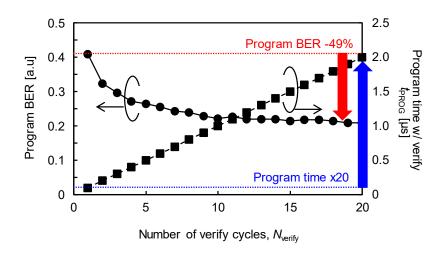

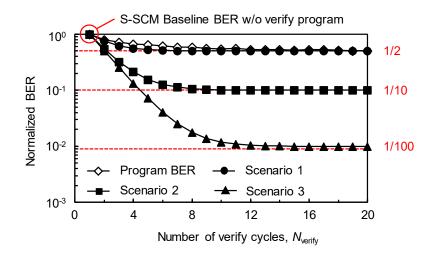

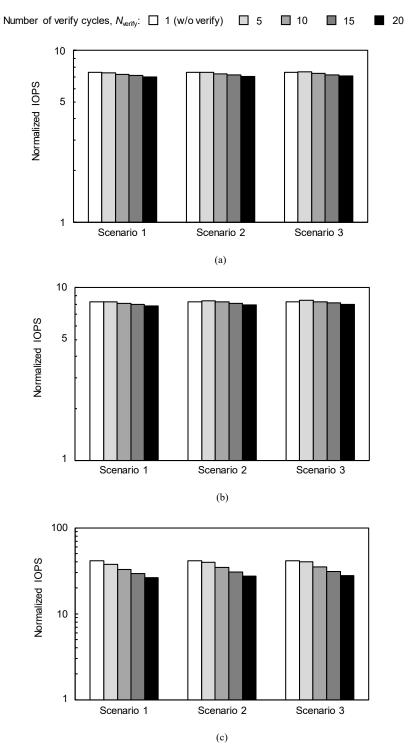

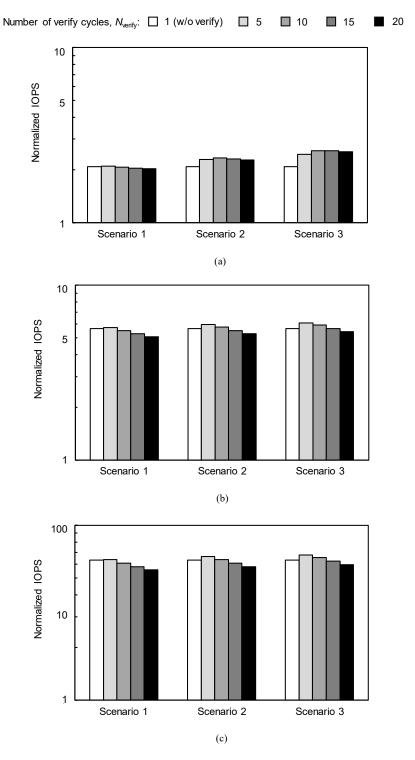

$$IOPS = \frac{\text{\# of read requests} + \text{\# of write requests}}{\text{Total consumption}}$$