# ゲートオールアラウンドナノワイヤトランジスタを用いた SRAM に関する研究 Study on SRAM by Gate-All-Around Nanowire Transistors

電気電子情報通信工学専攻 田村 誓亮

Seisuke Tamura

## 1. 研究目的

本研究の目的は、GAA-NW-SRAMの試作のための プロセス条件を検討することである。また、試作 GAA-NW-SRAMの設計最適化のために、ミックスシミ ュレーションのプラットフォームを作成する。

#### 2. 研究背景

近年、低消費電力化、集積化のために推し進めてきた MOS トランジスタの微細化が短チャネル効果の顕在化 により、従来の構造で微細化することが困難となってお り、微細化の指針であるムーアの法則を満たさなくなっ てきた。この微細化の障害が、高速メモリの1種、SRAM の性能向上の妨げとなり、情報保持の性能や消費電力の 改善に限界が訪れ、CPU の動作に対応することが困難と なった。そこで、ゲートオールアラウンドナノワイヤ (GAA-NW) 構造と呼ばれる次世代 3 次元構造を SRAM に応用することで、さらに微細化を進めることができる だけでなく、保持特性や消費電力の改善が期待できる。 先行研究のシミュレーションにて、性能を改善できるこ とが発表されているが[1]、実際に試作して実証しなけれ ばならない。試作 GAA-NW-SRAM の開発には、しきい 値電圧の制御方法の1つであるチャネルでの不純物注入 条件をGAA-NW構造と同じ膜厚で確認する必要がある。 ゆえに、本研究の目的として、しきい値電圧制御のプロ セス条件を、デバイスシミュレーションやプロセスシミ ュレーションで得た結果を適用した試作 SOI MOS トラ ンジスタの測定で検討する。また、今後の試作 GAA-NW-SRAM の開発のために、デバイスシミュレー ション、回路シミュレーションを融合したシミュレーシ

ョンを作成することを目的とする。

## 3. MOS トランジスタと SRAM の動作原理

## 3.1 MOS トランジスタの動作原理

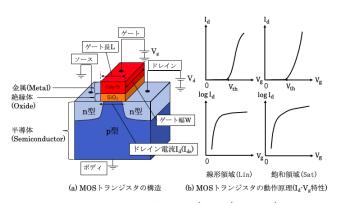

Fig.1 MOS トランジスタ(NMOS)

Fig.1(a)より、MOS トランジスタは、金属、酸化膜、 半導体の3種の材料から成り、ゲート、ソース、ドレイ ン、ボディの4つの端子を持つ。一定のドレイン電圧  $V_d$ を印加させた状態で、ゲート電圧  $V_g$ を変化させると、ド レイン-ソース間を流れる電流(ドレイン電流  $I_d$ )は、 Fig.1(b)のような特性が得られる。トランジスタがオンす るときの  $V_g$ をしきい値電圧( $V_{th}$ , $V_{thc}$ )といい、トランジス タのオン・オフの切り替わりの指標をサブスレッショル ド係数(SS)という。ドレイン電流において、電子が支配 的のときは NMOS トランジスタ、正孔のときは PMOS トランジスタと呼ばれ、PMOS では、Fig.1 の半導体部 分の極性(n型、p型)が入れ替わる。

#### 3.2 GAA-NW-MOS トランジスタの動作原理

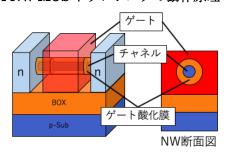

Fig.2 GAA-NW MOS トランジスタ(NMOS)

Fig.2 より、GAA-NW 構造は、ソース・ドレイン間に流れる部分(チャネル)がゲートに覆われており、従来の構造に比べて、さらに微細化、低消費電力化が可能で、ドレイン電流の制御性を改善できる構造として期待されている。

## 3.3 SRAM の動作原理

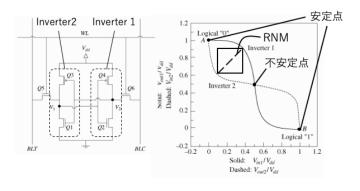

Fig.3 SRAM の回路と動作原理

Fig.3 より、SRAM(Static Random Access Memory)は、4つの NMOS、2つの PMOS で構成される回路で、中央の交差した CMOS インバータが電位の大きさで記憶保持として機能し、左右のトランジスタで記憶状態を読み取る。SRAM の特徴は、「読み取り」、「書き込み」、「保持」の3つの特性を持ち、WL、BLT、BLC の配線に印加する電圧でそれぞれの特性を制御する。本研究では、情報記憶としての役割で最も重要な保持特性に着目した。保持特性は Fig.3 の右図のように、インバータの入出力反転特性が2つ重なった特性(バタフライカーブ)を示す。情報の保持は、左右の安定点の  $V_a$  もしくは  $V_b$  の電位の大きさで判断する。情報を保持するには、外部のノイズによって保持された情報が変化しないようにする必要がある。その外部ノイズ耐性の指標を

RNM(Retention Noise Margin)で表し、バタフライカーブの中空に描かれる最大の正方形の対角線で算出される。この RNM を最も大きくする(高いノイズ耐性にする)には、エンハンスメント型( $V_{th}>0$  の MOS トランジスタ、PMOS の場合は  $V_{th}<0$ )の NMOS、PMOS の  $V_{th}$  をそれ

ぞれ一致させなければならない。

#### 4. デバイスシミュレーション

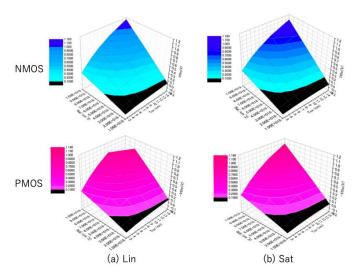

GAA-NW-SRAM の開発において、しきい値電圧の調整に必要な不純物注入条件はデバイスシミュレーションにて検討した。シミュレーションでは、NMOS: 0.1[V]、PMOS: -0.1[V]をしきい値電圧の目標値として設定し、実際の試作での構造を適用した GAA-NW-MOS トランジスタの 3D モデルを用いて、ゲート酸化膜  $T_{ox}$ とチャネル不純物濃度  $N_a(N_d)$ を変えたときのしきい値電圧の変化をシミュレーションした(Fig.4)。また、SS が最も良い  $T_{ox}$ =10[nm] のときの目標値が満たされる  $N_a(N_d)$ を Table.1 に示す。

Fig.4 Tox, Na(Nd)-Vthc 特性

Table.1 目標しきい値電圧を満たす N<sub>a</sub>(N<sub>d</sub>),SS

| T <sub>ox</sub> = | V <sub>d</sub> | $N_{a, d}$          | $V_{_{ m thc}}$ | SS10        |

|-------------------|----------------|---------------------|-----------------|-------------|

| 10[nm]            | [V]            | [cm <sup>-3</sup> ] | [V]             | [mV/decade] |

| NMOS              | 0.05 (Lin)     | 2×10 <sup>18</sup>  | 0.12            | 63          |

|                   | 1.2 (Sat)      | 3×10 <sup>18</sup>  | 0.15            | 63          |

| PMOS              | 0.05 (Lin)     | 2×10 <sup>18</sup>  | - 0.16          | -64         |

|                   | 1.2 (Sat)      | 2×10 <sup>18</sup>  | - 0.10          | -63         |

SS10 とは、 $I_d$ - $V_g$  特性において、 $I_d \times L/W = 10^{10}$  となるときの  $V_g$  の傾きの逆数を示す。

Table.1 より、目標しきい値電圧に最も近くなるチャネル 不純物濃度は、 $2\times10^{18} [{\rm cm}^{-3}]$ であり、このとき、SS は理 論限界値である  $60 [{\rm mV/decade}]$ 付近の値をとった。

## 5. プロセスシミュレーション

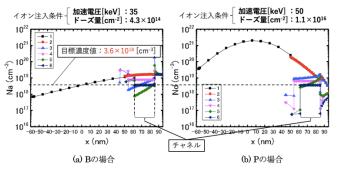

デバイスシミュレーションにて検討した濃度を試作デバイスに適用するには、NMOS、PMOS それぞれのチャネルに注入する B (ボロン)、P(UV)のドーズ条件も検討しなければならない。ドーズ条件とは、注入する不純物の量と注入するときの加速電圧の大きさである。不純

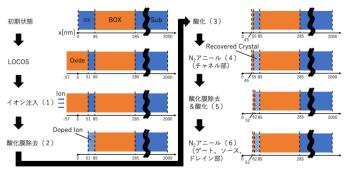

物濃度は、不純物の種類、温度や加速電圧で大きく変わるため、これらを考慮したプロセスシミュレーションを行い、ドーズ条件を正確に検討した(Fig.5.1)。

Fig.5.1 プロセスシミュレーションのイメージ図シミュレーションでは、B、Pが注入されたときのSOI(Silicon on Insulator, 平本・小林研究室のクリーンルームにて、GAA-NW 構造を作る際に必要なSOI 基板のBOX(埋め込み酸化膜)上Si)の深さに対して、Fig.5.1 (1)~(6)のプロセス経たときの濃度変化を確認し、Fig.5.1 (6)で不純物濃度の目標値を満たすドーズ量と加速電圧を検討した。不純物濃度の目標値は、実際の試作での誤差を考慮し、 $3.6 \times 10^{18} [{\rm cm}^{-3}]$ とした。これは、しきい値電圧が約0.3[V]となる濃度である。

Fig.5.2 不純物濃度分布の変化

Fig.5.2 より、B,P どちらもプロセスを経るにつれ、濃度が低下している。これは、酸化やアニールでの高温環境下でSi表面から不純物が抜け出ていくためである。また、SOI に着目すると、濃度分布のグラフは B では 凹型、Pでは凸型を示しているが、これは酸化によって Si が狭まり、Si 中の不純物が Si から押し出されたり、Si に取り込まれたりすることで濃度が部分的に変化するためである。

## 6. 試作デバイスの測定結果

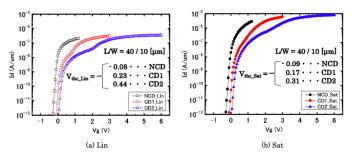

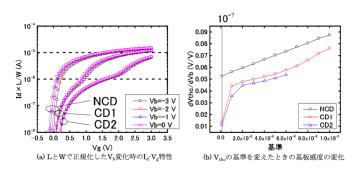

プロセスシミュレーションにて検討したドーズ条件で 試作した、CD1 デバイス、CD2 デバイス(CD1 の 2 倍 のチャネル不純物濃度)及びチャネルに不純物を注入し ていない、NCD デバイスの測定結果(Fig.6.1)から、チャ ネルの不純物注入によって  $I_d$ - $V_g$  特性が右にシフト、すな わち、しきい値電圧を動かし、エンハンスメント型の MOS トランジスタとして動作している様子が観測された。さらに、しきい値電圧を算出すると、0.1[V]もの小さい誤差で試作できた。

Fig.6.1 試作デバイスの Id-Vg 特性

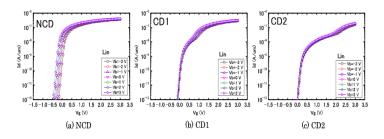

しかし、CD デバイス(CD1&CD2 デバイス)の  $I_d$ - $V_g$  特性において、一定の  $V_g$ を超えたとき、 $I_d$  が突然増加する現象が起きている。これは、しきい値電圧が異なる 2 つの MOS トランジスタが動作しているように見えているためである。この現象は、ボディに電圧を印加してしきい値電圧を操作する、基板バイアス効果の観測結果 (Fig.6.2)から推測した。

Fig.6.2 試作デバイスの基板バイアス効果

Fig. 6.2 より、 $I_d$ - $V_g$ 特性がボディ電圧  $V_b$ の変化に応じて、左右にシフトしているが、CD デバイス(Fig. 6.2(b),(c))のみ、 $I_d$ 増加前後で基板バイアス効果の有無が観測された。また、この基板バイアス効果の測定結果から、 $I_d$ 増加前後の基板感度(基板バイアス効果の効きやすさ)をしきい値電圧の基準を変えて算出した(Fig. 6.3)。

Fig.6.3 基板感度

一般的に基板感度は、NCD デバイスのように、基準を変えると線形的に変化するが、CD デバイスは、通常の定義方法の基準である 10<sup>-7</sup>とこれ以外の基準で大きく変化

していることがわかる。これが、1つの MOS トランジスタに2つの MOS トランジスタが動作していることを指し示している。

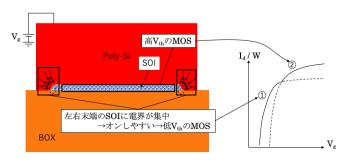

このような動作特性を示す原因は、SOI 断面の形状が台 形であることが考えられる(Fig.6.4)。

Fig.6.4 試作デバイスの動作原理

Fig.6.4 に示される SOI 断面の形状は、ソース・ドレイン間の形成の際に等方性エッチング(円形状に Si を削る工程)を行ったため、台形のような形状を示した。このような形状の場合、ゲート電圧を印加時に、左右末端の SOIで電界が集中するためにここで最初にオンし、ゲート電が増加していくと、中央の大きな割合を占める SOI が支配的になり、ドレイン電流が増加している現象が起きたと推測される。ゆえに、SOIの側面を垂直にエッチングする異方性エッチングでソース・ドレイン間を形成する必要がある。

## 7. ミックスシミュレーション

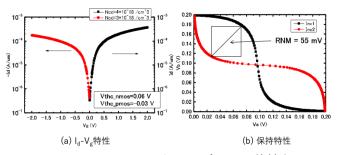

Fig.7 GAA-NW-MOS トランジスタの特性と RNM

試作 GAA-NW-SRAM の設計において、RNM を最適化するために、0.1 [V]付近の低いしきい値電圧かつ実際のプロセスで作られるデバイス構造の GAA-NW-SRAMを擬似的に再現し、TCAD シミュレーションと回路シミュレーションを組み合わせたミックスシミュレーションを行った(Fig.7)。目標値である 0.1 [V]を境に左右対称のバタフライカーブが描かれており、保持特性をシミュレーションすることができた。将来的に、このシミュレーションを用いて、様々なパラメータを変化させたときのRNM の変化をシミュレーションし、GAA-NW-SRAM の

設計・開発に活かすことができる。さらに、ばらつきの評価に応用することもできる。現在、RTN(Random Telegraph Noise)と呼ばれるしきい値電圧のばらつきを悪化させる問題が、GAA-NW MOSトランジスタの最も大きな課題となっており、この影響がRNMに対しても悪影響を及ぼすことが考えられる。ゆえに、このRTNの発生原因となるプロセスばらつきを再現したシミュレーション[2]と本研究で作成したミックスシミュレーションモデルを用いて、RNMのばらつきを評価できる。

#### 8. 結論

本研究では、GAA-NW-SRAM を試作する上で必要な 試作条件をシミュレーション、試作 SOI MOS トランジ スタの測定結果から検討した。また、試作デバイスの測 定結果から、不純物が注入されたソース・ドレイン間の SOI 断面が形状によっては、デバイス特性に悪影響を及 ぼすことが明らかになった。一方、ミックスシミュレー ションにて、GAA-NW-SRAM の保持特性を擬似的に再 現した。また、将来的に、ミックスシミュレーションと プロセスばらつきのシミュレーションと組み合わせるこ とで、しきい値電圧や RNM のばらつきを評価すること に応用できることを示した。

## 9. 今後の課題

今後の課題として2点挙げられる。1点目は、エンハンスメント型の PMOS の試作を完成させることである。本研究では、NMOS と PMOS を同時に試作したが、PMOS のみ動作しなかった。そのため、エンハンスメント型の PMOS を試作し、チャネル不純物のしきい値電圧のシフト変化を観察しなければならない。2点目は、試作を行う際に、SOI の断面形状を四角形にするエッチングを行い、左右末端の SOI がオンしないように防ぐ必要がある。

[1] Jiaojiao Ou, Ru Huang...et al, "Performance Investigation of SRAM Cells Based on Gate-all-around (GAA) Si Nanowire Transistor for Ultra-low Voltage Applications",

#### ICSICT2012,10.1109/ICSICT.2012.6466743

[2] Ramendra Singh, Kritika Aditya,...et al, "7-nm Nanowire FET Process Variation Modeling using Industry Standard BSIM-CMG Model", ICEE 2016, 10.1109/ICEmElec.2016.8074417